# standards d'interfaces

filtrage et protection contre leurtensions pour le bus I<sup>2</sup>C

Andreas Nadler (Würth Elektronik)

La communication des microcontrôleurs avec leurs périphériques fait souvent appel au bus I<sup>2</sup>C. Plus la distance de transmission augmente, plus le risque d'interférences est élevé. Grâce à un circuit adéquat de filtrage et de protection, on peut significativement améliorer l'immunité aux interférences.

Le bus I<sup>2</sup>C (*Inter-Integrated Circuit*) est une interface de communication série répandue, principalement utilisée pour connecter les microcontrôleurs avec les circuits intégrés (CI) périphériques (par ex. les capteurs ou la mémoire). Le bus utilise une ligne de données bidirectionnelle (SDA) et une ligne d'horloge (SCL). De plus, le bus ne se cantonne pas aux cartes, mais dans beaucoup d'applications on le prolonge aussi vers d'autres emplacements au moyen de divers connecteurs et câbles. Ceci rend le bus I<sup>2</sup>C plus sensible aux interférences externes telles que les décharges électrostatiques (ESD), les transitoires rapides en salves et le bruit RF rayonné. L'objet de cet article est de proposer au lecteur un circuit adapté de filtrage et de protection qui améliore l'immunité au bruit du bus I<sup>2</sup>C sans dégrader la qualité de signal des lignes de données et d'horloge. Pour cela, des modèles de simulation ont été créés sous LTspice et des mesures effectuées sur une application réelle afin de vérifier les résultats de la simulation.

## Topologie du bus I<sup>2</sup>C

Le bus I<sup>2</sup>C fonctionne sous le principe « maître/esclave », où le maître est toujours à l'initiative du transfert de données. C'est sa simplicité qui a fait le succès du bus. En revanche, le protocole est très basique et la topologie physique asymétrique. En pratique, ces deux facteurs font que le bus peut être très susceptible aux interférences externes (par ex. pendant les tests CEM). La **table 1** donne un aperçu des spécifications I<sup>2</sup>C.

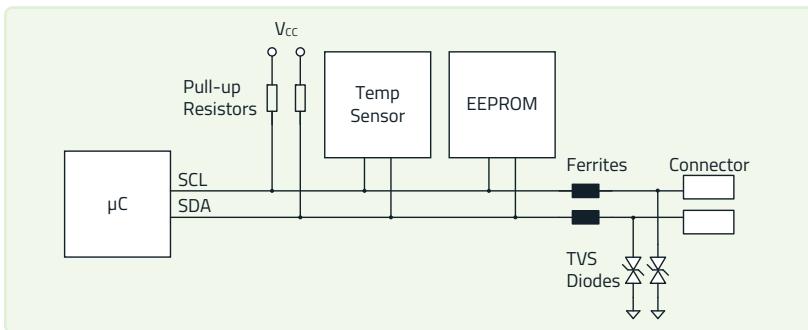

Tous les CI qui participent au bus I<sup>2</sup>C ont des sorties en collecteur commun (**figure 1** à gauche). Celles-ci commutent alternativement les résistances de rappel à la masse de référence et produisent ainsi les états logiques « 1 » ( $V_{CC}$ ) et « 0 » (GND). Comme le montre la **table 1**, les temps de montée maximum autorisés des fronts décroissent avec l'augmentation du débit de données. La relation mathématique entre les valeurs min et max des résistances de rappel est donnée par les **équations 1 et 2**.

$$R_{\text{Pullup\_min}} = \frac{(V_{CC} - V_L)}{I_{\text{Pullup}}} \quad (1)$$

$$R_{\text{Pullup\_max}} = \frac{t_r}{(0,8473 \cdot C_{\text{Bus}})} \quad (2)$$

$V_{CC}$  = Tension de référence du bus I<sup>2</sup>C (volt)

$V_L$  = Seuil logique « 0 » max (par ex. 0,4 V avec  $V_{CC} > 2$  V)

$C_{\text{Bus}}$  = Capacité parasite maximale du bus de l'application (farads)

$t_r$  = Temps de montée maximal autorisé en fonction du débit de données (secondes)

$I_{\text{Pull-up}}$  = Courant maximal possible au travers des broches de collecteur ouvert (ampères).

Combinées avec la capacité parasite du bus, les résistances de rappel [1] forment un étage RC. Ceci entraîne un retard des fronts de montée du signal carré. Dans beaucoup d'applications, cet étage RC est souvent ce qui détermine le maximum en termes de débit de données et de longueur de câble. Comme le montre la **table 1**, il en résulte pour la spécification I<sup>2</sup>C une capacité maximale du bus de 400 pF sous un courant de 3 mA pour les débits les plus fréquents (100 kbps et 400 kbps). Plus les valeurs

Table 1. Résumé des spécifications du bus I<sup>2</sup>C.

| Mode       | Horloge | Débit maxi | Temps de montée maxi<br>0,3 - 0,7 VCC | Capacitance maxi du bus | Courant maxi |

|------------|---------|------------|---------------------------------------|-------------------------|--------------|

| Standard   | 100 kHz | 100 kbit/s | 1000 ns                               | 400 pF                  | 3 mA         |

| Fast       | 400 kHz | 400 kbit/s | 300 ns                                | 400 pF                  | 3 mA         |

| Fast+      | 1 MHz   | 1 Mbit/s   | 120 ns                                | 550 pF                  | 20 mA        |

| High Speed | 3,4 MHz | 3.4 Mbit/s | 10 ns                                 | 100 pF                  | 3 mA         |

Figure 1. Schéma simplifié d'un bus I<sup>2</sup>C avec résistances de rappel (à gauche) et à droite avec ferrites et diodes TVS (à droite) comme protection pour améliorer l'immunité au bruit et réduire l'émission d'interférences.

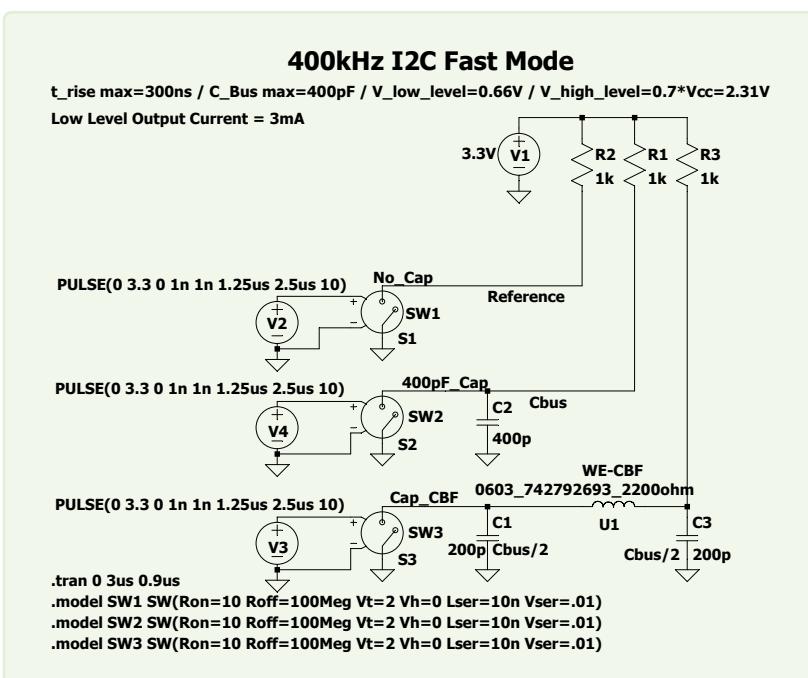

Figure 2. Schéma de la simulation LTspice avec 3 canaux : 0 pF, 400 pF et 400 pF + ferrite CMS multicouche.

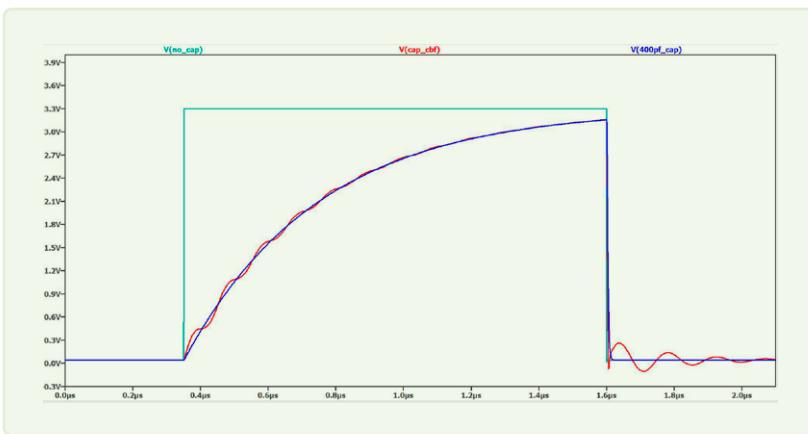

Figure 3. Résultat de la simulation LTspice dans le domaine temporel : 0 pF (turquoise), 400 pF (bleu) & 400 pF + ferrite CMS multicouche (rouge).

des résistances de rappel choisies sont faibles, plus le temps de montée des fronts peut diminuer. L'équation 1 montre que la limite inférieure détermine le seuil logique bas maximum, le niveau de tension de référence et le courant maximum possible.

La capacité parasite du bus dépend entre autres :

- Des capacités des composants

- Des longueur et largeur des pistes (environ 0,5 pF cm)

- De la longueur et du type des câbles et connecteurs

- De la structure des couches et de la constante diélectrique des circuits imprimés

## Choix des composants de filtrage et protection

Afin d'augmenter l'immunité à l'ESD, aux transitoires rapides en salves et rayonnement RF, on recommande une combinaison de ferrites CMS et de diodes TVS (figure 1 à droite). Les ferrites CMS à large bande (par ex. 742792693) augmentent continûment d'impédance au-dessus de 10 MHz et sont ainsi capables de protéger le bus contre les interférences RF. Les diodes TVS peuvent aussi détourner les surtensions vers la masse de référence.

Comme les valeurs des résistances de rappel sont souvent dans la gamme des kΩ, l'étage RC ainsi que l'impédance des ferrites CMS en-dessous de 10 MHz jouent ici un rôle mineur. On peut donc, dans un premier temps, considérer que le temps de montée du signal utile est peu influencé. Si on a choisi des diodes TVS à faible capacité (par ex. 824012823 - 0.18 pF), leur capacité n'a pas d'influence notable sur la qualité du signal. Pendant un test ESD par exemple, un courant de plus de 10 A peut circuler brièvement, ce qui produit une tension d'environ 10 V aux bornes de cette diode.

Tous les autres C1 sur le bus I<sup>2</sup>C doivent donc supporter cette tension. Cela ne fonctionne que si vous fournissez une masse à faible impédance (par ex. une grande surface de cuivre dans une couche interne) pour éviter une chute de tension supplémentaire.

## Simulation LTspice avec fréquence d'horloge de 400 kHz

Avec le programme de simulation gratuit LTspice, il est relativement facile d'étudier l'influence de la capacité parasite du bus en combinaison avec les résistances de rappel choisies. Pour un interrupteur piloté en tension, on sélectionne la fonction « Pulse » et on détermine la bande passante désirée selon la spécification I<sup>2</sup>C voulue. Pour la variante 400 kbps, la plus utilisée, on choisit une période de 2,5 µs. Pour un rapport cyclique de 50 %, on met la durée « high » à 1,25 µs. Pour profiter des 400 pF de maximum autorisé pour la capacité parasite du bus, les résistances de rappel sont fixées à 1 kΩ. On simule trois canaux (qui peuvent en pratique représenter SCL ou SDA).

- Sans capacité parasite du bus

- Avec 400 pF de capacité parasite du bus

- Avec 400 pF + ferrite CMS multilayer large bande (742792693).

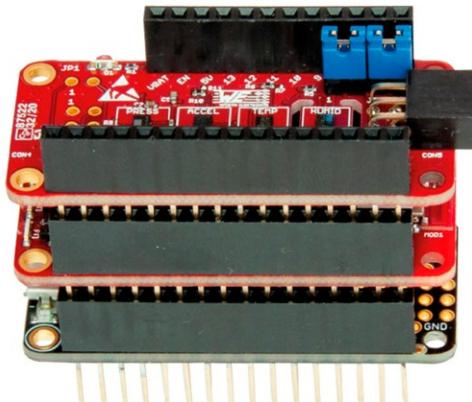

Figure 4. Kit SensorBLE FeatherWing de Würth Elektronik, composé de cartes microcontrôleur, Bluetooth et capteurs.

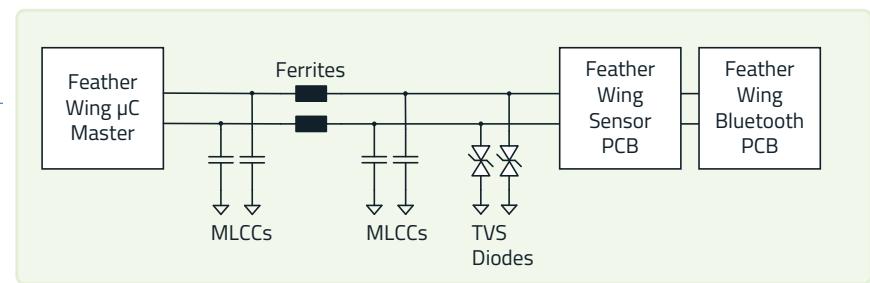

Figure 5. Schéma de la configuration de test avec le kit SensorBLE-FeatherWing de Würth Elektronik.

Le résultat de la simulation en **figure 3** montre que la ferrite CMS multicouche n'a pratiquement aucun effet sur le front montant du signal. Comme toute ferrite CMS multicouche a aussi une composante inductive, on observe des oscillations mineures en combinaison avec la capacitance du bus. Toutefois, celles-ci ne sont pas critiques car leurs amplitudes sont inférieures à 10 % du véritable signal utile.

### Mesures avec une application à 400 kHz de fréquence d'horloge

Pour vérifier la relativement simple simulation LTspice, des mesures complémentaires ont été effectuées avec un kit SensorBLE FeatherWing [2] de Würth Elektronik. Ce kit dispose d'une carte mère avec un microcontrôleur. Les deux autres cartes comportent un module Bluetooth WE et divers capteurs WE (accéléromètre 3 axes, température, humidité, pression – **figure 4**). La carte mère communique avec les deux autres via un bus I<sup>2</sup>C à un débit maximum de 400 kbps (**figure 5**). Les données des capteurs peuvent alors être affichées avec une application smartphone dédiée (par ex. WE-SensorBLE). On utilise des MLCC pour émuler une capacité parasite de 400 pF par rapport à GND. On a mis aussi la ferrite CMS multicouche (742792693) modélisée dans la simulation, ainsi qu'un réseau de diodes TVS (824012823). Un câble de 20 cm connecte la carte capteurs au reste du bus I<sup>2</sup>C. On trouve un arrangement de ce type dans de nombreuses applications.

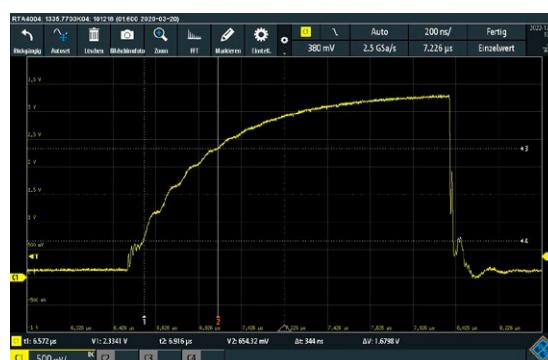

La courbe de tension sur la ligne SCL était mesurée en permanence. Les mesures [3] montrent des résultats pratiquement identiques à la simulation (**figure 6**). Le temps de montée ainsi que la qualité du signal ne sont pas dégradés par la ferrite CMS multicouche en combinaison avec la diode TVS. Le temps de montée du signal haut, qui est critique pour la synchronisation, ne dépend que de la capacitance du bus en combinaison avec les résistances de rappel choisies. Grâce à l'app du smartphone (WE-SensorBLE), on peut vérifier un fonctionnement sans erreurs dans les trois scénarios testés.

### Simulation et mesures en harmonie

La simulation aussi bien que les mesures montrent que les ferrites CMS en combinaison avec les diodes de protection ESD n'ont pas d'influence sur les signaux de données (SDA) et d'horloge (SCL) du bus I<sup>2</sup>C. Les résistances de rappel associées avec la capacité parasite du bus ont un fort impact sur la raideur des fronts des signaux. En contrepartie, cette combinaison de composants, diode de protection ESD et ferrite CMS à large bande, améliore l'immunité au bruit du bus I<sup>2</sup>C. En pratique, cela signifie en particulier une meilleure immunité à l'ESD, aux transitoires rapides en salves et au rayonnement RF.

230400-04

### À propos de l'auteur

Andreas Nadler est ingénieur électronicien diplômé d'état de la Kempten Technical School. Il a ensuite travaillé pendant plusieurs années comme ingénieur matériel dans le domaine des alimentations à découpage et la technologie des circuits analogiques. Depuis 2015, Nadler est ingénieur en applications de terrain chez Würth Elektronik eiSos GmbH, dans la division commerciale pour les composants actifs et passifs. C'est là qu'il se spécialise dans la conception des alimentations et interfaces conformes à la CEM, ainsi que sur la suppression globale des interférences des assemblages électroniques.

Figure 6. Mesure de référence avec résistances de rappel de 1 kΩ, ferrite CMS multicouche, réseau de diodes TVS, fils de 20-cm, et 400-pF MLCC (= 344 ns de temps de montée).

### LIENS

- [1] R. Arora, "I<sup>2</sup>C Bus Pullup Resistor Calculation," Application Report SLVA689, Texas Instruments: <https://ti.com/lit/an/slva689/slva689.pdf>

- [2] Kit SensorBLE Featherwing: [https://www.we-online.com/de/components/products/SENSOR\\_BLE\\_FEATHERWING\\_KIT](https://www.we-online.com/de/components/products/SENSOR_BLE_FEATHERWING_KIT)

- [3] A. Nadler, "Filter and surge protection for the I<sup>2</sup>C bus," Application Note ANP121: <https://www.we-online.com/ANP121>