# I'IA en développement électronique

une mise à jour après seulement un an

**Tam Hanna (Hongrie)**

Depuis l'introduction de Flux.AI, l'intelligence artificielle apporte une aide précieuse aux laboratoires d'électronique. Depuis notre dernière exploration des outils d'IA, le paysage a considérablement évolué. Voici donc une mise à jour concise pour vous présenter les derniers développements dans ce domaine.

Généralement, un article sur les systèmes IA offre seulement un aperçu momentané de leurs capacités, en raison de la dynamique évolutive de leur apprentissage. Ce qui est vrai aujourd'hui pourrait ne plus l'être demain. Il n'est donc pas étonnant que, seulement un an après notre dernier aperçu [1], il soit pertinent de revisiter les avancées récentes des outils IA dédiés au développement électronique. Les expériences décrites ici ont été réalisées à la fin du mois d'août 2024, et ne prennent donc pas en compte les développements ultérieurs.

## JITX ou un regard en coulisse

Les systèmes IA modernes se présentent généralement comme des boîtes noires. L'utilisateur soumet des requêtes et reçoit ensuite des

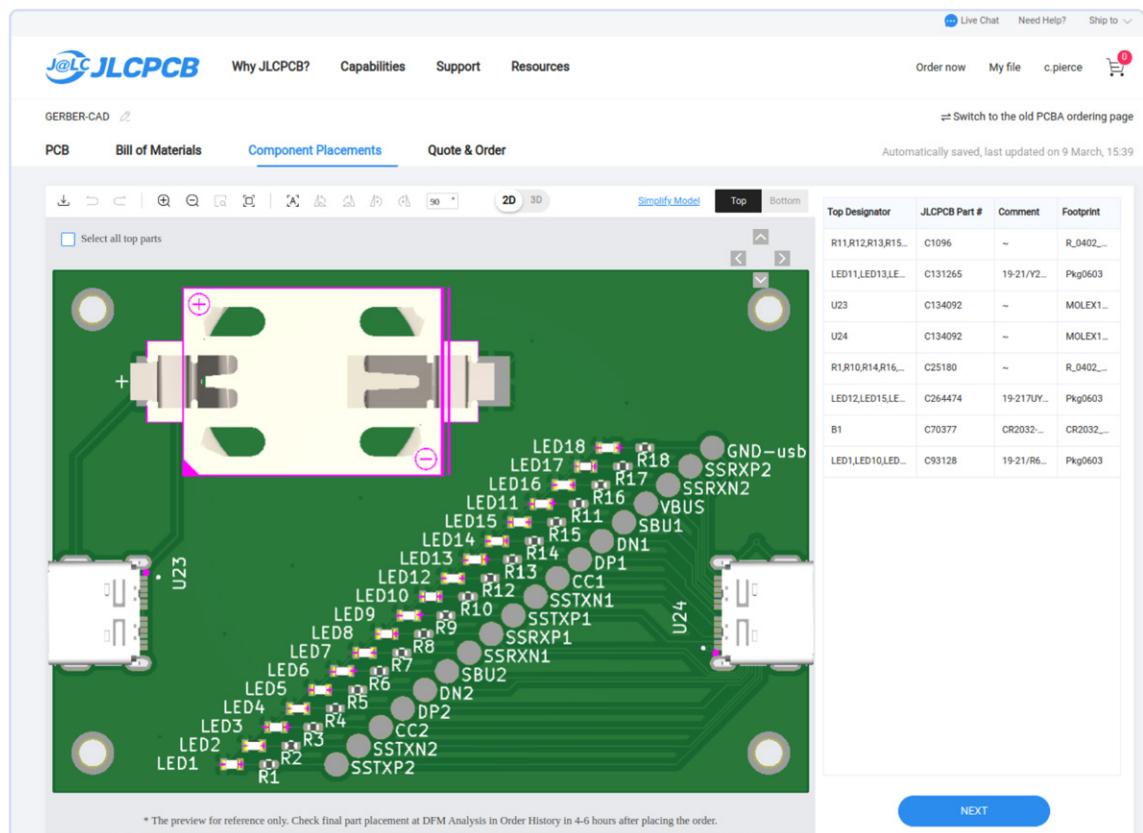

Figure 1. Cette carte peut être entièrement conçue avec des langages de programmation génératifs.

réponses qui varient en utilité. Les processus sous-jacents restent généralement cachés à l'utilisateur du système. Selon l'auteur, il existe dans de nombreux cas une représentation codée d'un circuit en arrière-plan.

Parmi les exceptions notables, JITX est l'une des rares entreprises à divulguer son langage de description textuelle. Pour explorer les coulisses, examinons le projet d'exemple fourni dans [2], un testeur de câble USB (**figure 1**). La création du port USB est détaillée par l'extrait de code suivant :

```

val usb-x-shift = 4.0

val usb-y-shift = -7.0

public inst in-usb :

components/USB-C-1054500101/component

place(in-usb) at loc((-1.0 * width(board-shape) / 2.0) +

usb-x-shift, usb-y-shift, -90.0) on Top

public inst out-usb :

components/USB-C-1054500101/component

place(out-usb) at loc((width(board-shape) / 2.0) -

usb-x-shift, usb-y-shift, 90.0) on Top

```

Les chaînes construites par `components/USB-C-1054500101/component` sont importantes ici, car elles correspondent au référentiel de composants respectif dans le système AI-EDA. Nous approfondirons ce sujet dans les étapes ultérieures. Pour l'instant, il est essentiel de noter que le positionnement des composants est réalisé ici au moyen de coordonnées saisies par l'utilisateur. Le système est donc incapable de calculer la position de manière autonome. Une fois les composants créés, il faut bien sûr les connecter. Avec l'interface USB utilisée ici, nous utilisons des « similitudes de noms » entre les broches des deux composants dans une boucle `for` structurée comme suit :

```

for p in pins(out-usb) do :

val pin-ref = ref(p)

```

```

val pin-name = tail(pin-ref, ref-length(pin-ref) - 1)

make-net(to-symbol(pin-name), [p])

```

Outre l'intégration de l'intelligence dans la conception du circuit, cette méthode offre l'avantage de faciliter le remplacement des objets grâce à la standardisation des empreintes de la bibliothèque. Ceci est même démontré dans le cas de la carte de test USB : La commutation entre deux jacks différents se fait en remplaçant la chaîne passée à la fonction générateur.

Concernant JITX, il faut noter qu'un plan gratuit [3] est disponible, qui, au moment de la rédaction de cet article, est limité à la création de designs open-source sous la licence CERN OHL-Permissive v2. Le fournisseur exclut explicitement l'utilisation de la GPL pour la conception résultante.

Il convient également de noter que JITX lui-même n'offre qu'un nombre comparativement faible de fonctionnalités d'IA. Le principal avantage est la possibilité d'inclure diverses contraintes dans les fichiers de conception, que le système applique ensuite automatiquement pour vérifier la tâche donnée.

## SnapMagic Copilot – A Star in the Electronics Sector

Le prochain participant à notre aperçu est SnapMagic, une évolution du célèbre service SnapEDA, qui se spécialise normalement dans la fourniture d'informations sur les composants pour les logiciels EDA tiers.

Un bon premier test consiste à rechercher un module radio Quectel relativement récent, un produit pour lequel la plupart des fournisseurs ne proposent pas encore d'empreintes. La force principale de *SnapMagic Search*, le nom sous lequel le service est désormais connu, est évidemment sa capacité à s'intégrer à une vaste gamme de logiciels EDA.

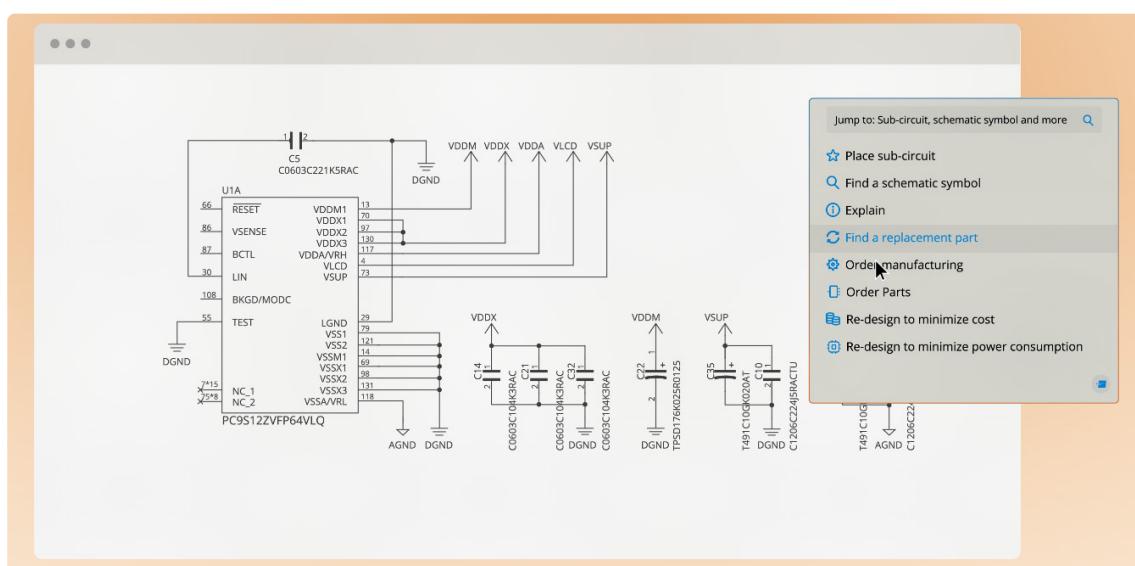

Avec un nouveau service appelé SnapMagic Copilot, actuellement en phase bêta fermée, SnapMagic vise à étendre ces fonctions. Il s'agit d'un système IA qui accepte les requêtes en langage naturel

Figure 2. SnapMagic Copilot communique en langage naturel pour exporter les résultats vers les logiciels EDA existants.

et propose ensuite des circuits de base exportables pour un large éventail de systèmes EDA.

Dans ses démonstrations, l'entreprise montre également comment « construire une structure de soutien » : par exemple, le copilote est capable d'analyser une fiche technique et d'ajouter automatiquement les condensateurs nécessaires pour assurer le fonctionnement sécurisé d'un circuit intégré. Toutefois, il est dommage que la liste d'attente [4] pour accéder à ce service soit actuellement complète - à la date de clôture de la rédaction de cet article, la demande d'admission de l'auteur n'a pas été approuvée.

Ce qui est intéressant avec SnapMagic, c'est que l'introduction de l'assistant IA est considérée comme un moyen permettant d'offrir des « services à valeur ajoutée. » La **figure 2** montre que SnapMagic aspire également à prendre en charge l'approvisionnement en composants.

### CircuitMind : un savoir-faire fonctionnel solide

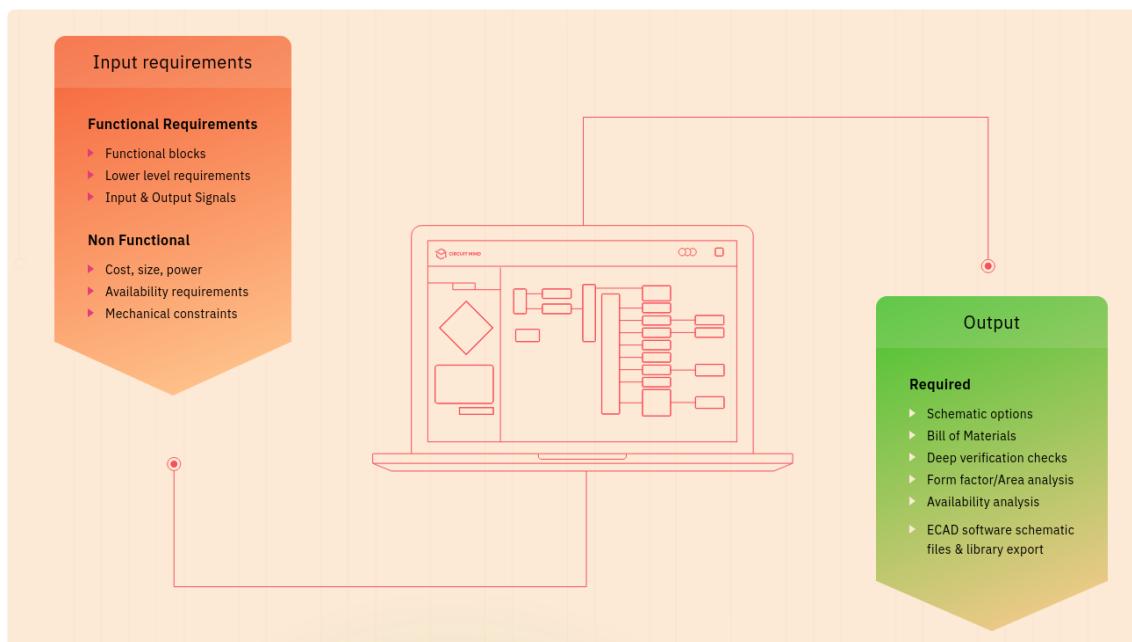

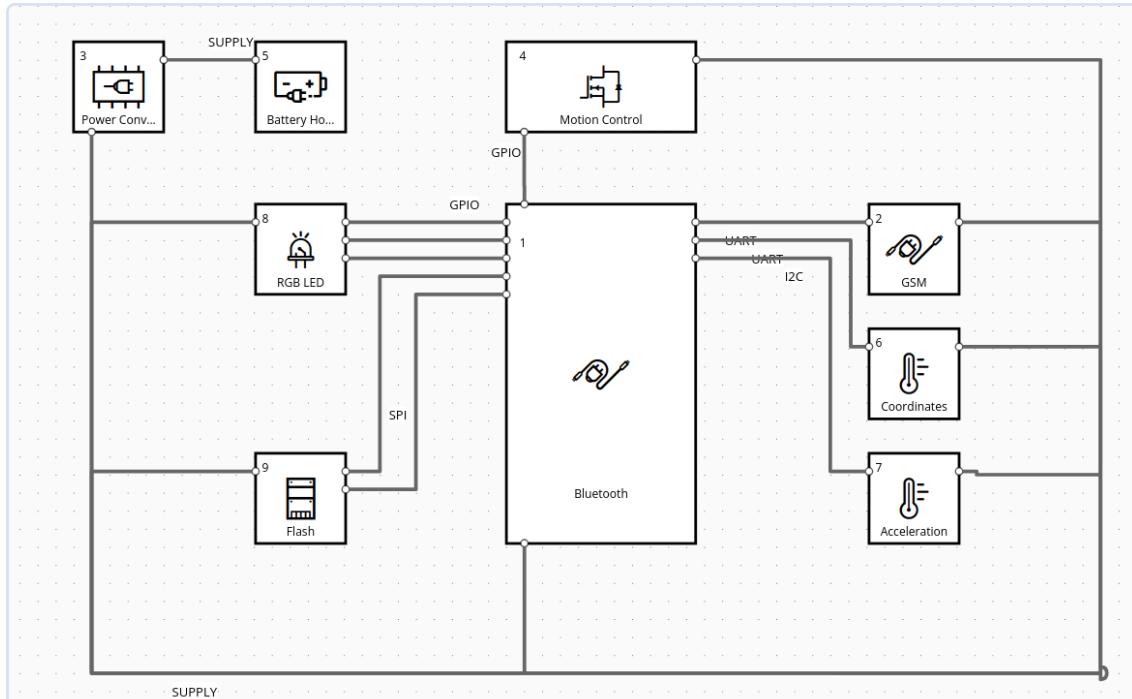

CircuitMind vise à libérer l'utilisateur des tâches puis - comme le montre le schéma de CircuitMind [5] (voir **figure 3**) - à les convertir en circuits ou en tâches de circuits. Le développeur est censé entrer des contraintes et des interfaces qui décrivent le plus exactement possible la conception du circuit à générer par l'intelligence artificielle.

Sur le site web de CircuitMind, les utilisateurs doivent d'abord créer un compte sur le site web en saisissant un nom d'utilisateur et un mot de passe. Ensuite, un système de prise de rendez-vous est proposé pour organiser des démonstrations en direct. Lors des tests effectués par l'auteur, les rendez-vous se sont avérés assez faciles à obtenir, avec des disponibilités même pour le jour ouvrable suivant. L'auteur a été personnellement accueilli par le fondateur de l'entreprise, Tomide Adesanmi. L'ancien employé de BAE Systems a souligné que la lecture des fiches techniques est l'une des tâches

les plus ennuyeuses auxquelles un développeur électronique doit faire face au cours de sa carrière.

Le produit d'Adesanmi se distingue comme un outil d'automatisation de la conception de systèmes évitant délibérément de se positionner dans le marché concurrentiel des EDA. Le système vise plutôt à générer des circuits et leurs variantes, optimisées selon différents paramètres, et de les comparer les unes avec les autres automatiquement.

En arrière-plan, le système repose sur une architecture composée de deux éléments. Le premier élément est une base de données de composants appelée *Commodore*, qui répertorie les modèles des composants connus du système. 70 % de la base de données est créée automatiquement, tandis que le reste est saisi et vérifié manuellement, mobilisant une part significative des ressources de l'équipe de développement. Le second élément, appelé *Ace*, est chargé de concevoir des circuits et leurs variantes à partir des objectifs de conception (*design goals*) et des données contenues dans *Commodore*.

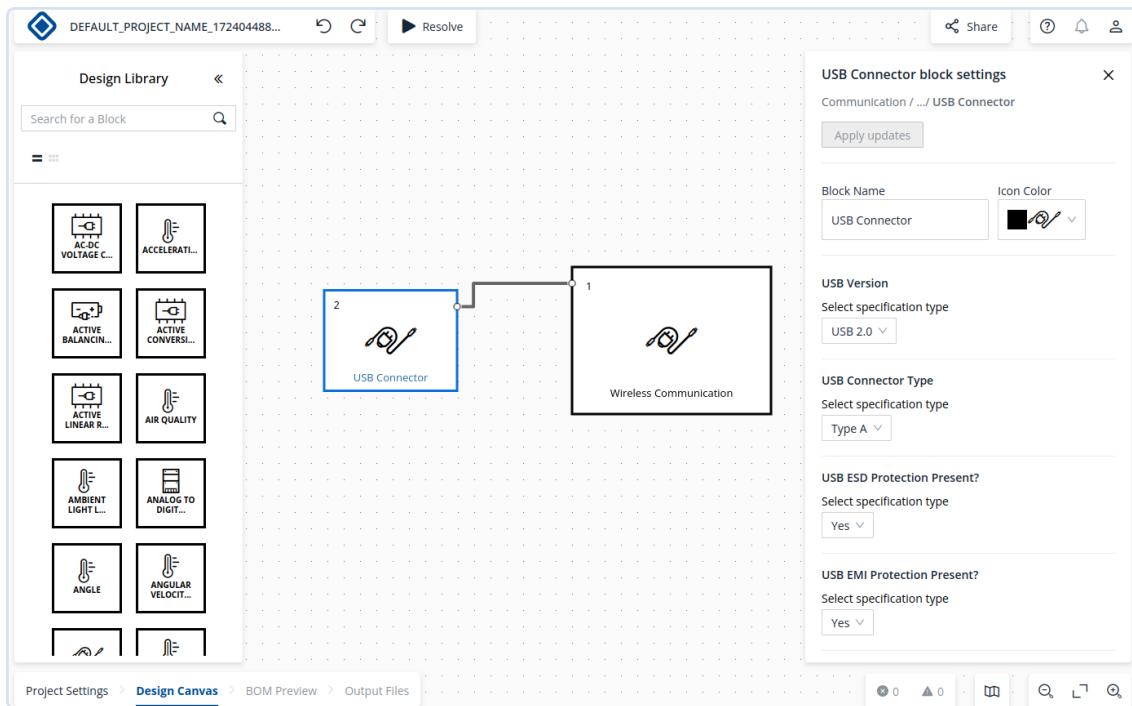

Il est intéressant de noter que ce processus de synthèse est géré par une « IA classique, basée sur des règles ». Au cours de la discussion, Adesanmi a souligné à plusieurs reprises que leur système n'utilise pas de grands modèles linguistiques (LLM), préférant une approche moins sujette aux erreurs dites d'hallucination typiques des LLM. Quoi qu'il en soit, le véritable avantage est une vue appelée *Solution Exploration*. La **figure 4** montre ce que les concepteurs peuvent visualiser grâce à cet outil.

Dans ce cas, il est évident que les variantes générées diffèrent notamment en termes de taille de la carte et de coûts matériels prévus.

En cliquant sur les différents champs, les utilisateurs peuvent générer une variété de documents essentiels : Outre une nomenclature interactive, qui permet d'analyser les différents coûts,

Figure 3. CircuitMind prend en charge la conception au niveau fonctionnel.

| Compare Solutions |                                           |                                      |                                      |                        |                        |

|-------------------|-------------------------------------------|--------------------------------------|--------------------------------------|------------------------|------------------------|

|                   | Size/Cost/Power                           | BOM                                  |                                      |                        |                        |

| Ref               | Solution                                  | Tradeoffs (Size / Price / Power)     | Size                                 | Price                  | Power                  |

| ●                 | <b>3. Power Optimised</b><br>7 months ago | <b>0% / 0% / 100%</b><br>100 boards  | <b>828.12 mm<sup>2</sup></b><br>+55% | <b>\$27.40</b><br>+46% | <b>14mW</b><br>-94%    |

| ●                 | <b>2. Cost Optimised</b><br>8 months ago  | <b>0% / 100% / 0%</b><br>100 boards  | <b>836.42 mm<sup>2</sup></b><br>+57% | <b>\$13.65</b><br>-27% | <b>242.6mW</b><br>+10% |

| ○                 | <b>1. Balanced</b><br>8 months ago        | <b>33% / 33% / 33%</b><br>100 boards | <b>534.41 mm<sup>2</sup></b><br>0%   | <b>\$18.73</b><br>0%   | <b>219.6mW</b>         |

Figure 4. L'exploration des solutions vous permet de comparer les avantages et les inconvénients de différentes circuits.

le système génère des documents d'interface et divers autres fichiers qui peuvent être utiles pour la certification, par exemple. Cette solution relativement onéreuse, dont le prix de départ avoisine les 10 000 US dollars, a captivé l'auteur par une fonctionnalité particulièrement innovante : la capacité du système à intégrer des « blocs analogiques » dans le processus de synthèse. Ces blocs agissent comme des espaces réservés adaptés à différentes conceptions électroniques ou circuits généraux. Le système les incorpore alors au cours du processus de conception, même lorsque les composants qu'ils contiennent demeurent méconnus.

## Celus : De la « Rich Data Sheet » à la génération automatique de circuits

Les générateurs automatiques de circuits sont un exemple frappant de l'intégration de l'IA dans le domaine de l'électronique. Des systèmes tels que Red Expert de Würth, Mindi de Microchip ou le système de conception en ligne de Texas Instruments offrent depuis longtemps la possibilité de saisir des paramètres et de recevoir en retour des schémas de circuits détaillés incluant des recommandations pour les composants passifs.

Avec le format CUBOs, décrit en détail dans [6], Celus propose une fiche technique numérique qui est soutenue depuis un certain temps par le spécialiste autrichien de l'électronique de puissance RECOM. Pour démarrer avec Celus, il suffit de visiter leur site Web [7], où il est possible de créer un compte directement sur le serveur du fournisseur ou via une authentification avec un compte LinkedIn ou Google. Optant pour cette dernière option, l'auteur a suivi le processus et, après avoir renseigné son niveau de formation et ses intentions d'utilisation, a été redirigé vers l'interface connue sous le nom de *Design Studio*. Cependant, la plateforme propose également un assistant à plusieurs niveaux pour une introduction plus facile. La saisie des configurations est intéressante. Initialement, un texte structuré comme le montre la **figure 5**, apparaît où le développeur est invité à remplir divers champs avec les informations nécessaires. Dans les deux étapes suivantes, une configuration supplémentaire est nécessaire ; dans le domaine des systèmes EDA supportés, seul le triumvirat Altium, Eagle et KiCad sont actuellement pris en charge. Après cette phase, il est possible de sélectionner un modèle prédéfini qui récapitule les configurations nécessaires pour les tâches fréquentes.

### Project Summary

This project aims to achieve this application goal. It will do these things. It should work this way. This comprises of these functions and requirements. It should operate under these power conditions. It should meet these standards and regulations. It must work within this operating environment and under these constraints and limits. The project cost is expected to be under this budget. Parts are sourced from these manufacturer(s). The expected outcome of this project is these outputs and outcomes.

Figure 5. Ce texte à remplir est la première étape vers un projet opérationnel.

Cependant, lors d'un test où l'auteur a tenté de concevoir un module radio 4G basé sur un chipset Quectel, le système n'a malheureusement proposé aucune suggestion. En récompense de vos efforts, un espace de travail apparaît qui, comme le montre la **figure 6**, a été clairement inspiré par des classiques tels que Microsoft Visio.

À l'extrême gauche de l'interface, une boîte à outils permet au développeur de sélectionner les *Prefabs* qui représentent les fonctions du circuit. Ces éléments peuvent être glissés et déposés dans la zone de conception au milieu et connectés à d'autres unités fonctionnelles en ajoutant des broches. En outre, la plupart des unités fonctionnelles offrent des options supplémentaires accessibles via un clic droit sur l'élément concerné. Par exemple, pour le connecteur USB, il est possible de choisir d'inclure des protections contre l'inversion de polarité ou les décharges électrostatiques dans le design actuel.

Une fois le travail effectué, un clic sur le bouton *Resolve* affiché en haut permet idéalement d'obtenir un dessin fonctionnel. Dans le cas de la conception illustrée à la Figure 6, le système a émis un message d'erreur indiquant que des CUBO n'existaient pas : Manifestement, l'auteur avait assigné « trop » de contraintes au connecteur USB, ce qui explique pourquoi la bibliothèque (limitée) n'a pas pu trouver de composants appropriés.

Pour explorer d'autres possibilités, retournez à la page d'accueil, où vous trouverez des exemples de projets de Renesas et STMicroelectronics. Le « Ultra Low Power Pet Tracker » semble intéressant dans la mesure où il devrait en principe contenir également une interface radio. La récompense de cet effort est la conception illustrée à la **figure 7**, où il est intéressant de noter que certaines des

Figure 6. Toute ressemblance entre Celus et Visio est purement fortuite...

connexions ont ici des call-outs rappelant Visio, qui décrivent le « type » de connexion à établir entre les éléments.

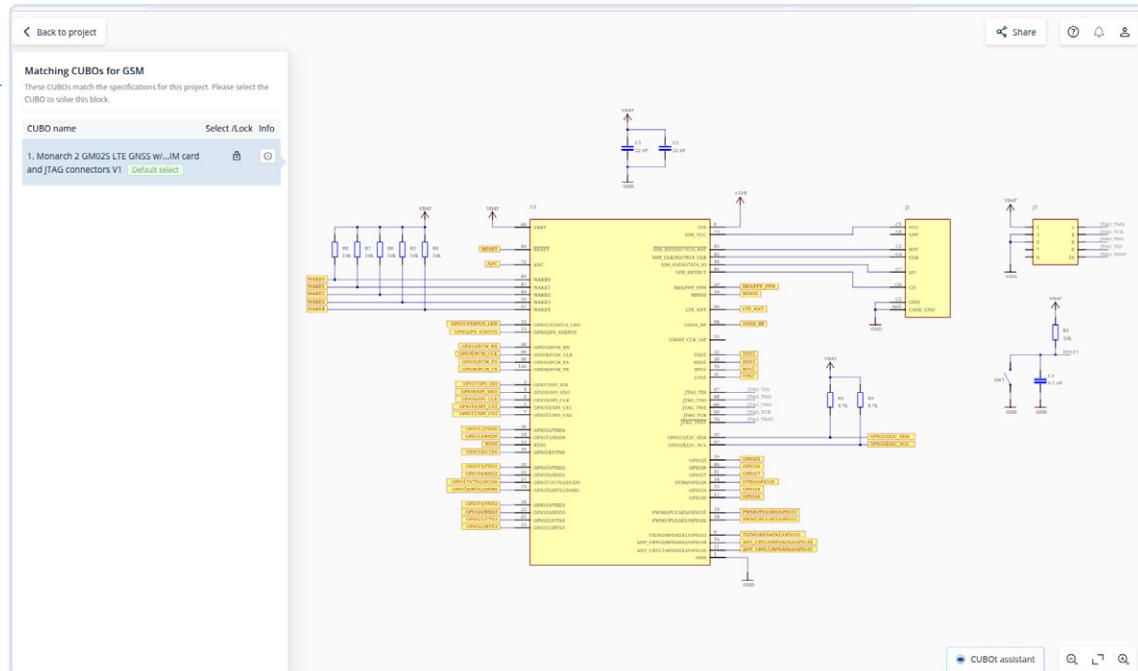

L'étape suivante consiste à cliquer sur le bouton *Resolve*, après quoi un symbole de robot apparaît, qui, en plus de jongler avec des Rubik's cubes, indique également que la recherche de divers CUBO appropriés est en cours. Après la première itération du processus de recherche, des points bleus apparaissent dans le coin supérieur droit des différents objets de construction, indiquant que Celus souhaite proposer des « candidats à la mise en œuvre » pour ces composants. Un clic droit sur le point ouvre alors un menu contextuel dans lequel l'option correspondante peut être sélectionnée. Dans le cas

du GSM-CUBO, par exemple, un seul objet est proposé, comme le montre la **figure 8**. Un clic sur le symbole Lock permet alors de déterminer un objet souhaité.

Après avoir sélectionné quelques composants, un nouveau clic sur le bouton *Ressources* est nécessaire, qui fournit maintenant un certain nombre de « Livrables ». L'auteur a trouvé particulièrement intéressant le rapport de projet, qui peut être téléchargé pour ce projet à l'adresse [8]. Si vous disposez d'une licence Altium, vous pouvez également charger le projet dans Altium par la suite et l'adapter à vos besoins. Il est intéressant de noter que Celus ne s'occupe pas de la tâche particulièrement délicate qui consiste à

Figure 7. Le projet d'exemple « Traceur d'animaux de compagnie à très faible consommation » dans Celus.

*Figure 8. La sélection des modules radio GSM est modeste.*

générer la configuration du circuit imprimé. Au lieu de cela, le logiciel ne génère que le schéma, la liste des pièces et le fichier de projet ; l'entreprise semble laisser la conception finale au développeur et à sa créativité.

## Recherche automatisée d'erreurs dans les projets matériels

Ce que Lint est pour le programmeur C, Cady veut l'être pour le développeur électronique. Selon la documentation officielle, le système ne prend en charge que les formats Altium, Xpedition et

OrCAD - mais selon les « informations générales » à [9], il prend également en charge Eagle et KiCad. Il convient également de noter que la société propose une option d'essai gratuit « de base ». Toute personne qui s'enregistre avec l'adresse électronique de son entreprise peut accéder au système - il convient toutefois de noter que cette variante n'évalue que les diagrammes de conception fournis par l'entreprise.

Le résultat de ces efforts est la création d'une « table d'erreurs », comme le montre la **figure 9**. Il est frappant de constater que Cady reconnaît à la fois les erreurs fréquentes et celles qui le sont moins -

| Index   | Part Reference | Pin Number | Nets        | Components                    | Category                                     | Description                                                                                             | Status                          |

|---------|----------------|------------|-------------|-------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------|

| 1       | C136           | 1          | NetC135_1   | 04024C102KAT2A                | Potential Capacitor Breach                   | Voltage difference of 5V is larger than the rated voltage 4V                                            | <span>...</span> <span>▼</span> |

| 2       | U14            | 1          | VDD_3V3     | LTC2997HDCB#TRMPBF            | Connection Instruction Violation             | a Capacitor connected between this pin and D- should have a value of 470pF                              | <span>...</span> <span>▼</span> |

| + 3-4   | ...            | 17         | ...         | MIC22705VML-TR                | Connection Instruction Violation             | a Capacitor connected between this pin and Ground should have a value of 2.2uF                          | <span>...</span> <span>▼</span> |

| 5       | C1             | 1          | 3V3_F       | 06036D476MAT2A                | Potential Capacitor Breach                   | Voltage difference of 3.3V is too close to the rated voltage 6.3V<br>50% derating factor is recommended | <span>...</span> <span>▼</span> |

| + 6-7   | ...            | 1          | ...         | CC0402KRX5R5BB225             | Potential Capacitor Breach                   | Voltage difference of 3.3V is too close to the rated voltage 6.3V<br>50% derating factor is recommended | <span>...</span> <span>▼</span> |

| 8       | R32            | 2          |             | RC0603FR-0712K1L              | Invalid Passive Component Connection         | This pin should not be left floating                                                                    | <span>...</span> <span>▼</span> |

| 9       | U14            | 4          | VDD_1V8     | LTC2997HDCB#TRMPBF            | Invalid Supply Voltage                       | Supply voltage 1.8V is out of operating range (2.5V to 5.5V)                                            | <span>...</span> <span>▼</span> |

| + 10-20 | U7             | ...        | VCORE_FPGA  | XCT7AT5T-1CSG324I             | Invalid Supply Voltage                       | Supply voltage 1.7V is out of operating range (0.87V to 1.05V)                                          | <span>...</span> <span>▼</span> |

| + 21-22 | U7             | ...        | VCORE_FPGA  | XCT7AT5T-1CSG324I             | Invalid Supply Voltage                       | Supply voltage 1.7V is out of operating range (0.92V to 1.05V)                                          | <span>...</span> <span>▼</span> |

| 23      | U18            | 1          | GND         | TPS62080ADSGT                 | Activity Level Violation                     | Active HIGH ENABLE pin should not be connected to the Ground                                            | <span>...</span> <span>▼</span> |

| 24      | U3             | 32         | RBIAS       | LAN8740A-EN-TR                | Connection Instruction Violation             | This pin should be connected to Ground via a Resistor                                                   | <span>...</span> <span>▼</span> |

| 25      | U19            | 4          | NetL15_1    | LT1764AEQ-3.3#TRPBF           | Connection Instruction Violation             | This pin should be connected to Ground via a Capacitor                                                  | <span>...</span> <span>▼</span> |

| 26      | Y2             |            |             | RH100-25.000-10-F-2030-EXT-TR | Oscillator Violation <span>New!</span>       | Connected load capacitance should have a value of 10pF                                                  | <span>...</span> <span>▼</span> |

| 27      | U15            | 1          | D+          | FT234XD-T                     | Differential Lines                           | Potential mismatch - N type pin connected to P type net                                                 | <span>...</span> <span>▼</span> |

| 28      | U15            | 12         | D-          | FT234XD-T                     | Differential Lines                           | Potential mismatch - P type pin connected to N type net                                                 | <span>...</span> <span>▼</span> |

| + 29-30 | U1             | ...        | ...         | STM32F427VIT7TR               | Missing Pull Resistor                        | Pull-up resistor is missing                                                                             | <span>...</span> <span>▼</span> |

| 31      | U7             | b10        | NC_U7_b10   | XCT7AT5T-1CSG324I             | Floating Power Pin                           |                                                                                                         | <span>...</span> <span>▼</span> |

| 32      | U18            |            |             | TPS62080ADSGT                 | Thermal Pad Connection Instruction Violation | This component's Exposed Pad must be connected to GND,<br>yet it does not appear in the netlist         | <span>...</span> <span>▼</span> |

| + 33-34 |                | ...        |             |                               | Calculation Mismatch <span>New!</span>       | Net name implies 1.8V while calculated voltage from U16 (MIC22705VML-TR) is 2.34V                       | <span>...</span> <span>▼</span> |

| 35      | U12            | t2         | DDR3_RESETn | MT41K256M16TW10T1T            | Best Practice                                | It is recommended to add a capacitor to Ground on reset pins for multiple purposes                      | <span>...</span> <span>▼</span> |

| + 36-37 |                | ...        |             |                               | Best Practice                                | Missing Test Point                                                                                      | <span>...</span> <span>▼</span> |

*Figure 9. L'analyse de Cady se révèle assez pédante.*

Figure 10. La start-up reste discrète sur les coûts engendrés par l'utilisation de Cady.

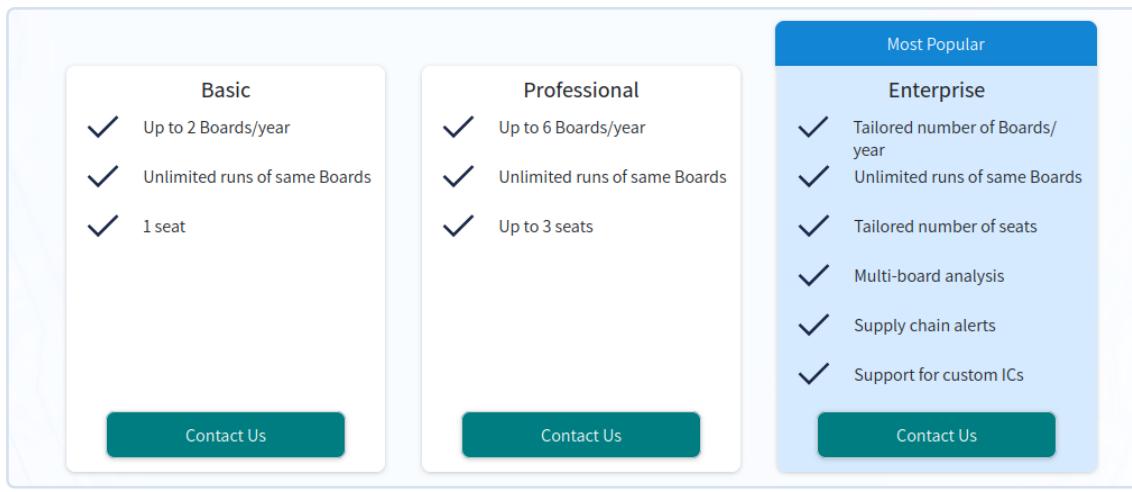

et, bien sûr, la startup promet également de continuer à apprendre de nouveaux tours au système. Un point de critique est que la tarification du système n'est pas du tout transparente. Au lieu de cela, comme le montre la **figure 10**, l'entreprise promet trois niveaux de prix, où il convient de noter que les « cartes » mentionnées ici couvrent chacune un design.

### Un fournisseur de services complets avec de nouvelles fonctionnalités

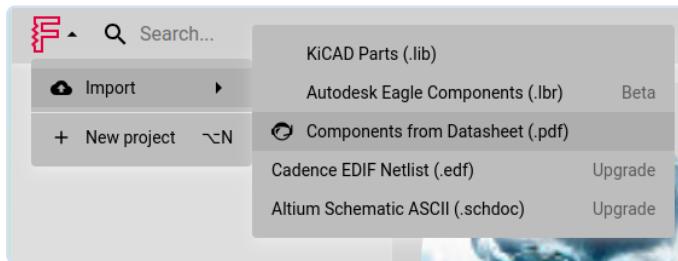

Flux.AI [10] détient une place unique en tant que seul fournisseur de services complets d'EDA. Bien que nous ayons déjà exploré ce service en détail dans [1], de nouvelles fonctionnalités ont été introduites récemment. Cet article présente brièvement ces ajouts, témoignant de l'évolution continue de la plateforme.

Figure 11. Cette fonction permet d'économiser quelques heures de travail.

Figure 12. Après avoir téléchargé le fichier PDF, il faut faire preuve d'un peu de patience.

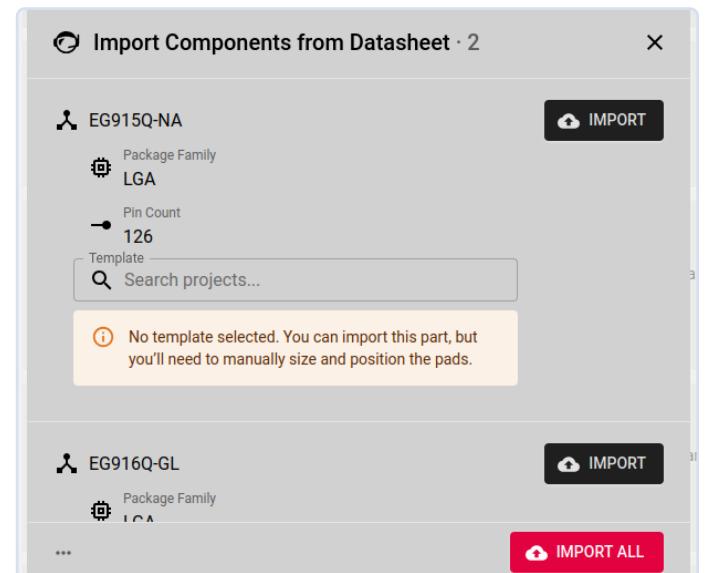

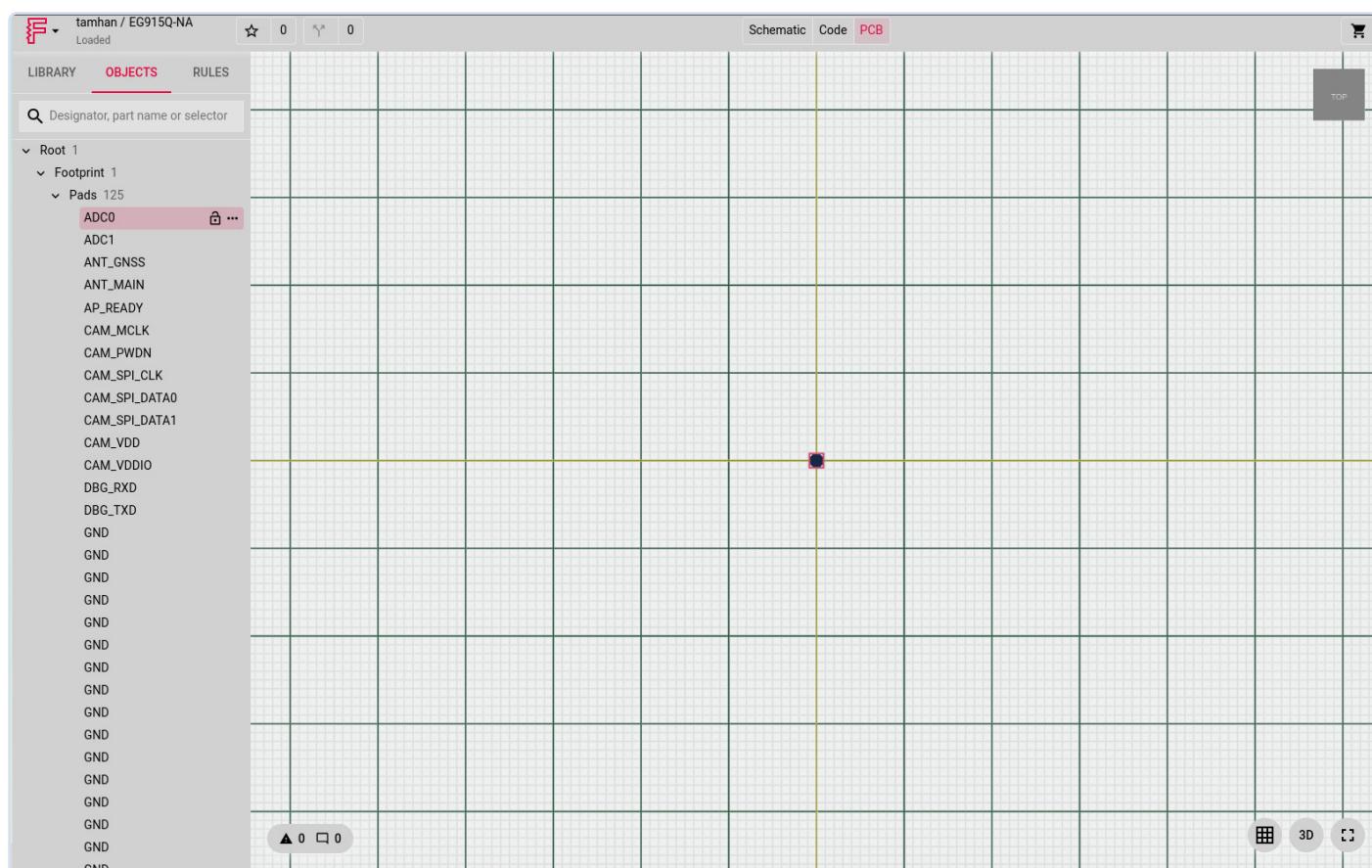

Une des fonctionnalités marquantes de Flux.AI est intégrée dès le menu de démarrage, comme le montre la **figure 11**. Le service peut désormais identifier automatiquement les empreintes des composants directement à partir des fiches techniques au format PDF. Pour tester cette capacité, l'auteur a utilisé un module Quectel 4G. Le téléchargement d'un fichier d'environ 2 Mo a activé la « boîte de dialogue de progression » visible dans la **figure 12**. Même avec la version de base gratuite, en environ cinq minutes, le système a réussi à reconnaître et analyser les composants listés dans la fiche technique, comme illustré dans la **figure 13**, démontrant ainsi l'efficacité de l'analyseur PDF.

### Relativement coûteux !

Un compte gratuit offre 50 crédits par mois. L'utilisation du module radio Quectel en a utilisé 31, et l'importation a consommé les crédits restants.

Figure 13. Ce résultat d'analyse est assez impressionnant.

*Figure 14. Le symbole du schéma de circuit semble quelque peu manquer d'inspiration...*

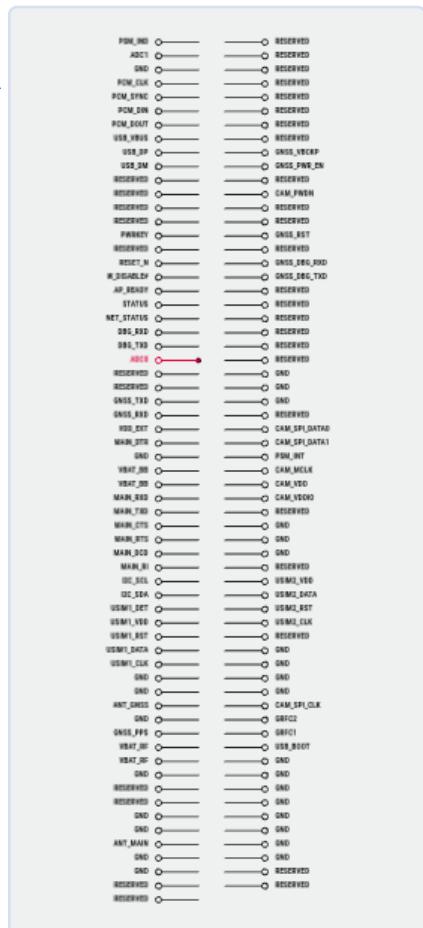

Cependant, après l'importation proprement dite, la désillusion s'est installée. Comme le montre la **figure 14**, le système n'a pas été en mesure de déterminer l'empreinte « réelle ». Des améliorations sont également possibles dans le domaine des schémas de circuit - voir la **figure 15** à titre d'exemple.

L'optimisation de la fabrication est une autre caractéristique essentielle : le système analyse la nomenclature pour trouver des moyens de réduire les coûts. Une fonction qui fonctionne généralement bien, selon l'auteur, est la rationalisation des composants passifs : le système recherche des composants similaires et utilise l'heuristique de l'IA pour déterminer s'ils peuvent être consolidés en une seule UGS afin de simplifier la nomenclature et de réduire les coûts de fabrication.

Les suggestions d'optimisation des composants, en revanche, sont parfois moins raisonnables. Par exemple, une entreprise qui utilise beaucoup de propriété intellectuelle de STMicroelectronics ne sera pas forcément emballée par la recommandation présentée dans la figure 16. En outre, le système génère divers documents de conception sur demande, y compris un schéma fonctionnel (généralement encombré) avec les différents composants, et aide à créer une stratégie de mise en service qui, par exemple, assiste un fabricant sous contrat dans l'examen des assemblages réalisés. Enfin, Flux.AI s'intègre dans le processus de développement logiciel

Figure 15. ... tandis que l'empreinte est une invitation à le faire soi-même.

Figure 16. Malheureusement, il n'y a pas non plus de solution miracle en électronique.

pour les projets basés sur le runtime MicroPython. En plus d'exporter des documents de support, le système est également capable de vérifier l'exactitude du code du micrologiciel dans la fenêtre Copilot en fonction des possibilités via son LLM.

Outre les optimisations de performance, l'accent sera probablement mis ici sur le matériel mal configuré, un exemple classique étant la sélection d'une adresse I<sup>2</sup>C incorrecte pour un capteur thermique.

## L'ordinateur comme électronicien : entre mythe et réalité

Il est difficile de concevoir un domaine où il est aussi facile de lever des fonds. Présentez un projet basé sur l'intelligence artificielle à des investisseurs en capital-risque, et vous recevrez très probablement un financement rapide. L'expansion du marché, avec non seulement Flux.AI mais aussi des dizaines d'autres entreprises qui se lancent, témoigne d'une évolution significative dans le domaine de l'intelligence artificielle appliquée à l'électronique. Cependant, il reste à questionner la portée pratique de ces avancées.

Selon l'auteur, nous sommes encore loin de l'ère du « PC électronicien » capable de fournir des conceptions entièrement finies sans besoin de révisions supplémentaires. Néanmoins, l'utilisation appropriée des différents générateurs et systèmes de débogage peut déjà économiser un temps précieux si ces outils sont intégrés de manière judicieuse et mesurée dans le processus de développement. ↗

240451-04

## Questions ou commentaires ?

Envoyez un courriel à l'auteur ([tamhan@tamoggemon.com](mailto:tamhan@tamoggemon.com)), ou contactez Elektor ([redaction@elektor.fr](mailto:redaction@elektor.fr)).

## À propos de l'auteur

Ing. Tam Hanna a plus de 20 ans d'expérience dans l'électronique, l'informatique et le développement logiciel. Il est développeur indépendant, auteur et journaliste ([www.instagram.com/tam.hanna/](https://www.instagram.com/tam.hanna/)). Dans ses moments de loisir, il se passionne pour l'impression 3D et la vente de cigarettes.

## Produits

- Peter Dalmaris, *KiCAD Like A Pro (Bundle)*, (Elektor 4th edition)

Livre : [www.elektor.fr/20942](https://www.elektor.fr/20942)

E-Book (PDF) : [www.elektor.fr/20943](https://www.elektor.fr/20943)

## LIENS

- [1] Tam Hanna, "l'IA dans les laboratoires d'électronique", Elektor 11/2023 : l'IA dans les laboratoires d'électronique

- [2] USB cable tester : [https://github.com/JITx-Inc/jitx-cookbook/tree/main/usb\\_c\\_cable\\_tester](https://github.com/JITx-Inc/jitx-cookbook/tree/main/usb_c_cable_tester)

- [3] JITx versions and costs : <https://www.jitx.com/plans>

- [4] SnapMagic waiting list : <https://www.snapmagic.com/#join>

- [5] Circuit Mind : <https://www.circuitmind.io/>

- [6] What are CUBOs? : <https://www.celus.io/cubos>

- [7] Celus: <https://www.celus.io/>

- [8] Rapport du projet (PDF) : <https://www.elektormagazine.fr/240451-04>

- [9] Getting started with Cady: <https://cadysolutions.com/how-to-use-cady/>

- [10] Flux.AI : <https://www.flux.ai/>