# HDI au milieu

Un nouveau service PCB-pooling rentable pour des petits BGA

## contribué par Eurocircuits

Parfois, il y a un composant que nous voulons vraiment utiliser, mais il n'est disponible que dans un boîtier BGA à pas fin – l'utiliser ferait basculer notre conception au-delà de la « technologie PCB standard » vers le domaine HDI. HDI signifie techniquement « interconnexion à haute densité », et pratiquement, cela signifie que nous pouvons concevoir avec des isolements plus petits et des traces plus fines. De plus, nous pouvons utiliser des « microvias » : des via avec des pastilles plus petites et des diamètres de trous plus

petits que ce qui est normalement possible avec un perçage mécanique.

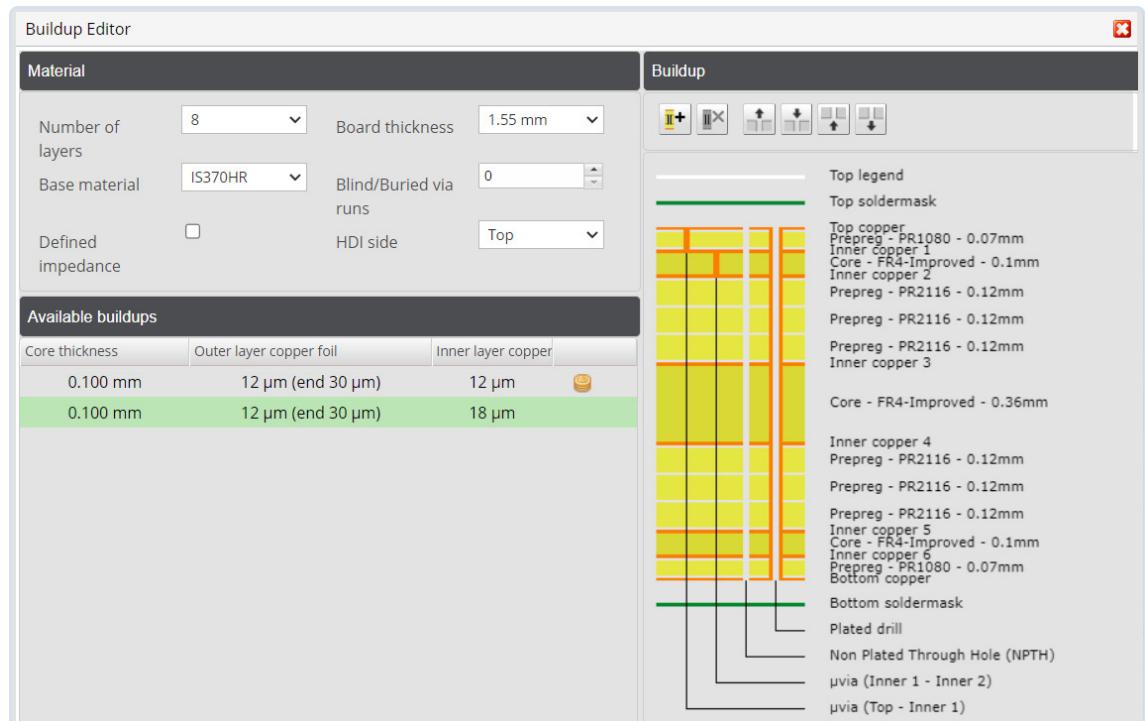

Le HDI permet la miniaturisation, ce qui est formidable, mais cela peut être gênant si cela nous est « imposé » par un seul petit composant sur tout un PCB, rendant ainsi la fabrication excessivement chère. Chez Eurocircuits, nous avons la solution – « au milieu » – qui peut aider nos clients à gérer à la fois l'ennui et le coût. Notre HDI pool (**figure 1**), une construction en 8 couches, conserve les classes techniques « technologie standard » telles quelles, et ajoute des microvias

Figure 1. Notre empilage 8 couches de HDI pool

**Pattern classification**

|                                                                    | 7      | 8    | 9    |      |

|--------------------------------------------------------------------|--------|------|------|------|

| Copper clearance, any layer                                        | $\geq$ | 125  | 100  | 90   |

| Pad diameter, outer layers<br>Add this value to NPTH diameter      | $\geq$ | +350 | +300 | +300 |

| Pad diameter, inner layers<br>Add this value to NPTH diameter      | $\geq$ | +350 | +350 | +300 |

| Clearance from PTH, inner layers<br>From hole edge                 | $\geq$ | 250  | 250  | 250  |

| Clearance from NPTH, inner layers<br>From hole edge                | $\geq$ | 200  | 200  | 200  |

| HDI microvia pad diameter<br>Available only for layers 1-2 and 2-3 | $\geq$ | 280  | 230  | 210  |

| HDI microvia diameter<br>Available only for layers 1-2 and 2-3     | =      | 100  | 100  | 100  |

**Hole diameter classification**

|                                         | A      | B    | C    | D    | E    |

|-----------------------------------------|--------|------|------|------|------|

| Plated through-hole (PTH) diameter      | $\geq$ | 500  | 350  | 250  | 150  |

| Non-plated through-hole (NPTH) diameter | $\geq$ | 600  | 450  | 350  | 250  |

| Max PCB thickness (mm)                  | =      | 3.20 | 3.20 | 2.40 | 2.00 |

|                                         |        |      |      |      | 1.60 |

entre les couches 1-2 et 2-3 ou entre 8-7 et 7-6. Cela permet à nos clients de concevoir avec ces BGA à pas fin, où le coût reste gérable puisque le « HDI » est limité à une petite zone et à deux passages de microvias.

**En pratique**

Que signifie cela en pratique ? Prenons la classe technique 7 avec la classe de perçage E de la **figure 2**, où le plus petit diamètre de pastille possible est de 0,45 mm (0,1 + 0,35 mm) ; cela ne rentre pas dans la plupart des diamètres de pastille de BGA à pas fin. Cependant, lorsque nous utilisons la même classification avec le HDI pool, le plus petit diamètre devient 0,28 mm, ce qui conviendra ! Cela permet aux concepteurs de placer des vias au centre des pastilles de BGA sans avoir à agrandir les pastilles au-delà des recommandations du fabricant. Les pastilles de microvia plus petites signifient également que l'utilisation des motifs dogbone devient une possibilité.

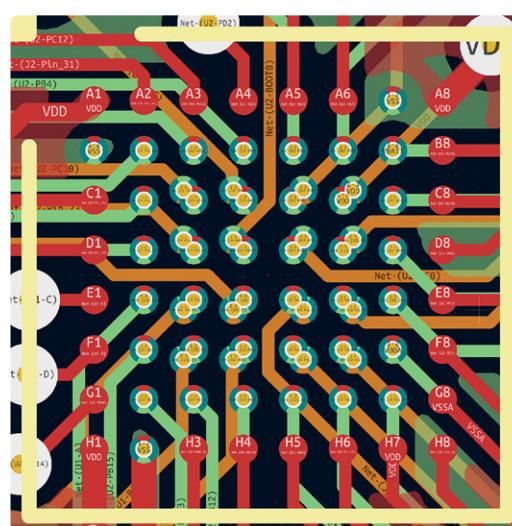

Évidemment, il est impossible de couvrir toutes les matrices de broches BGA et leurs configurations pour déterminer quelle partie sera routable et laquelle ne le sera pas. Cependant, nous avons configuré nos paramètres pooling de manière à ce que les matrices 8×8 soient entièrement routables pour les BGA jusqu'à un pas de 0,4 mm. (La **figure 3** montre un exemple d'une matrice 8×8 à pas de 0,4 mm entièrement connectés.) Mais bien sûr, des matrices plus grandes sont également possibles, et cela dépend de la taille de la matrice, de la configuration des broches et de

la manière dont ces broches sont utilisées. Dans de nombreux boîtiers, il y a des broches « No Connect », et dans la plupart des conceptions, toutes les broches d'un microcontrôleur ou d'un processeur ne sont pas utilisées, ce qui peut faciliter le routage de grandes matrices BGA avec seulement deux passages de microvias.

Que faire maintenant ? Nous vous invitons à télécharger vos conceptions dans notre Visualizer [1] et à les vérifier pour leur fabriabilité. Comme toujours, nous accueillons vos retours sur la manière dont ce service peut résoudre vos problèmes de fabrication. ↗

240593-04

Figure 2. Les paramètres de nos classes techniques pour lesquels le regroupement HDI est disponible (notez que la classe 9 n'est pas pooling.)