**ELEKTOR**

## +PC-PLUS:

- interface de mesure universelle •

- micrologger connectable au PC •

- câbles de liaison pour PC •

*moniteur

de lignes

TV*

ELEKTOR

a

EDUCATEC

du 24 au 28 novembre

Hall : 7-1

*inclinomètre*

## audio-DAC 2000

*haut de gamme à 96 kHz/24bits*

**ADSL:

surfer

à

TGV**

# SOMMAIRE

## INFORMATIONS

### 20 ADSL, accès haute vitesse à Internet

Avec jusqu'à 8 Mbits/s, ADSL ouvre de nouvelles perspectives d'accès à Internet par le biais d'une ligne téléphonique ordinaire.

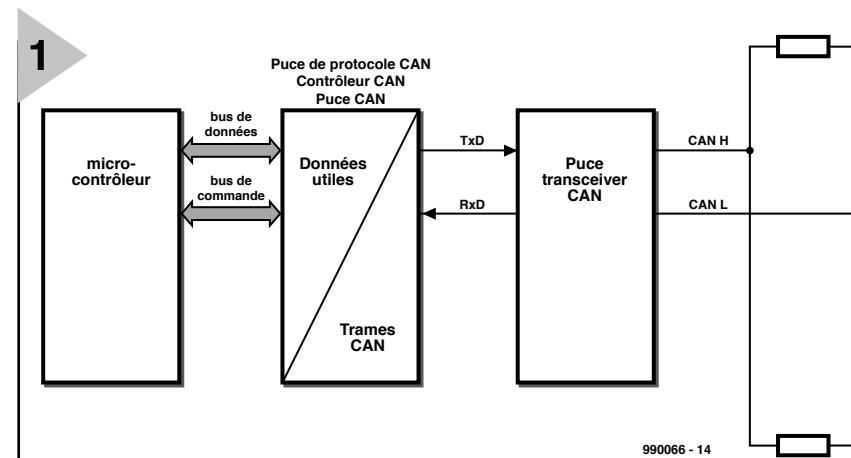

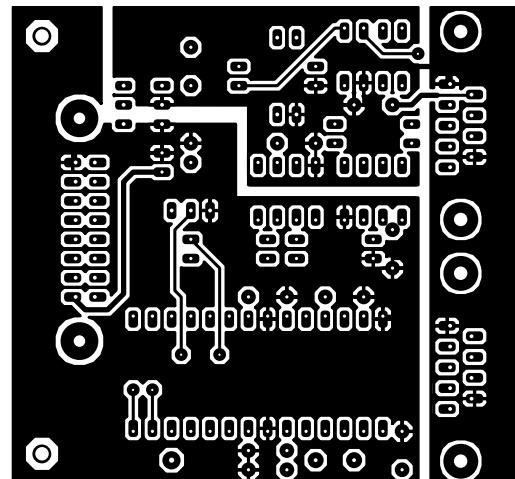

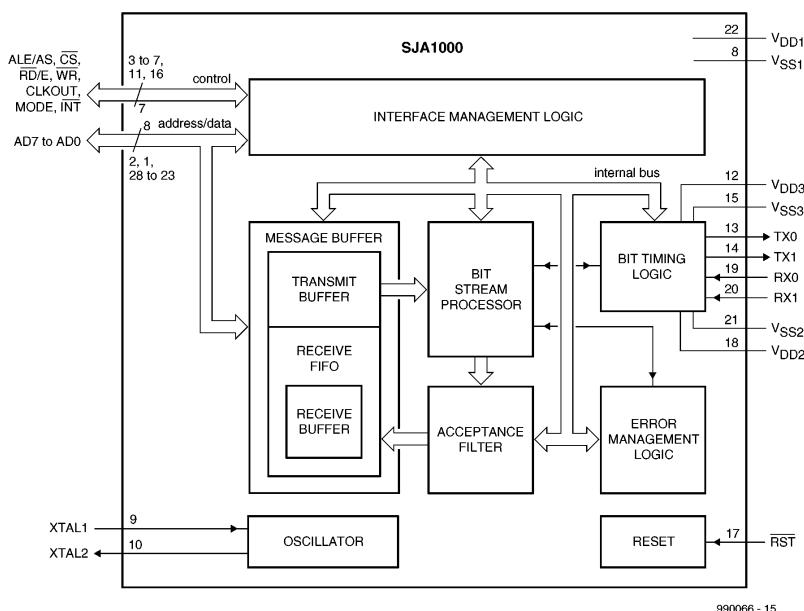

### 58 le bus CAN (3)

communication de données futée pour spécialiste (3<sup>e</sup> partie)

Nous passons aujourd'hui à la réalisation pratique d'un système bâti autour d'un bus CAN.

## RÉALISATIONS

### 14 audio-DAC 2000 (1)

#### convertisseur N/A pour l'amateur de perfection

Cette version haut de gamme peut travailler à une résolution de 24 bits et une fréquence d'échantillonnage de 96 kHz.

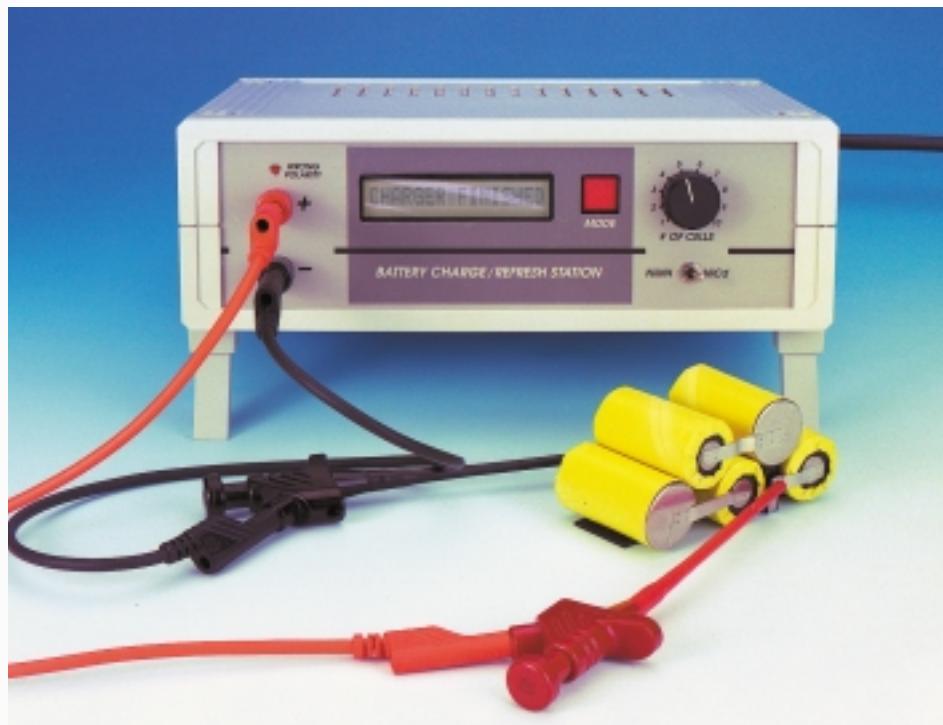

### 26 chargeur d'accus HP (2)

#### construction, étalonnage et mode d'emploi

Piloté par 68HC05, ce chargeur est à même de charger de 1 à 10 cellules CdNi ou NiMH.

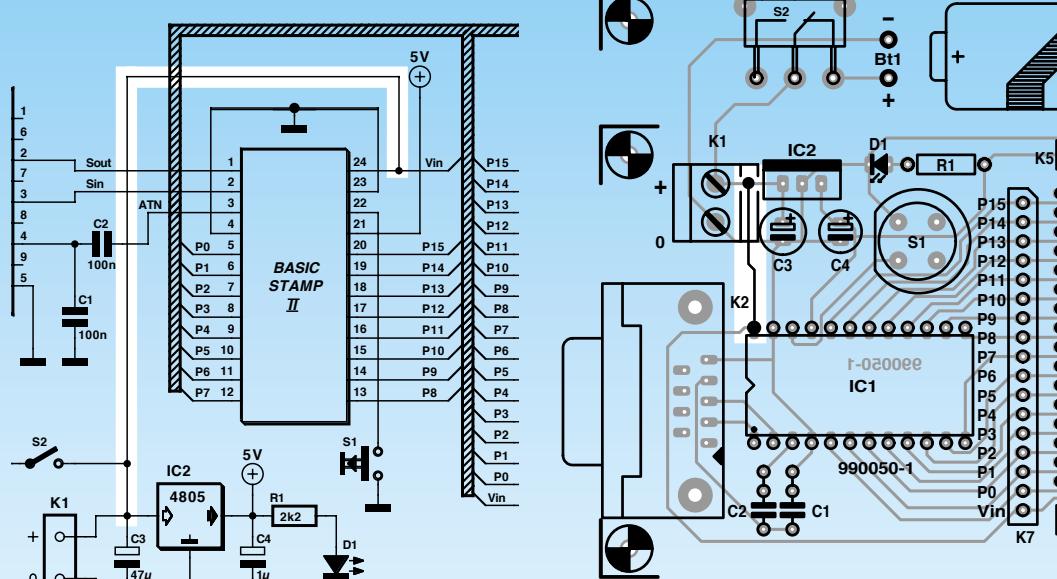

### 32 cours de programmation du BASIC Stamp (3)

#### 3<sup>e</sup> partie : programmation en BASIC

Cet article présente les instructions de branchement et d'accès à l'EEPROM du BASIC Stamp.

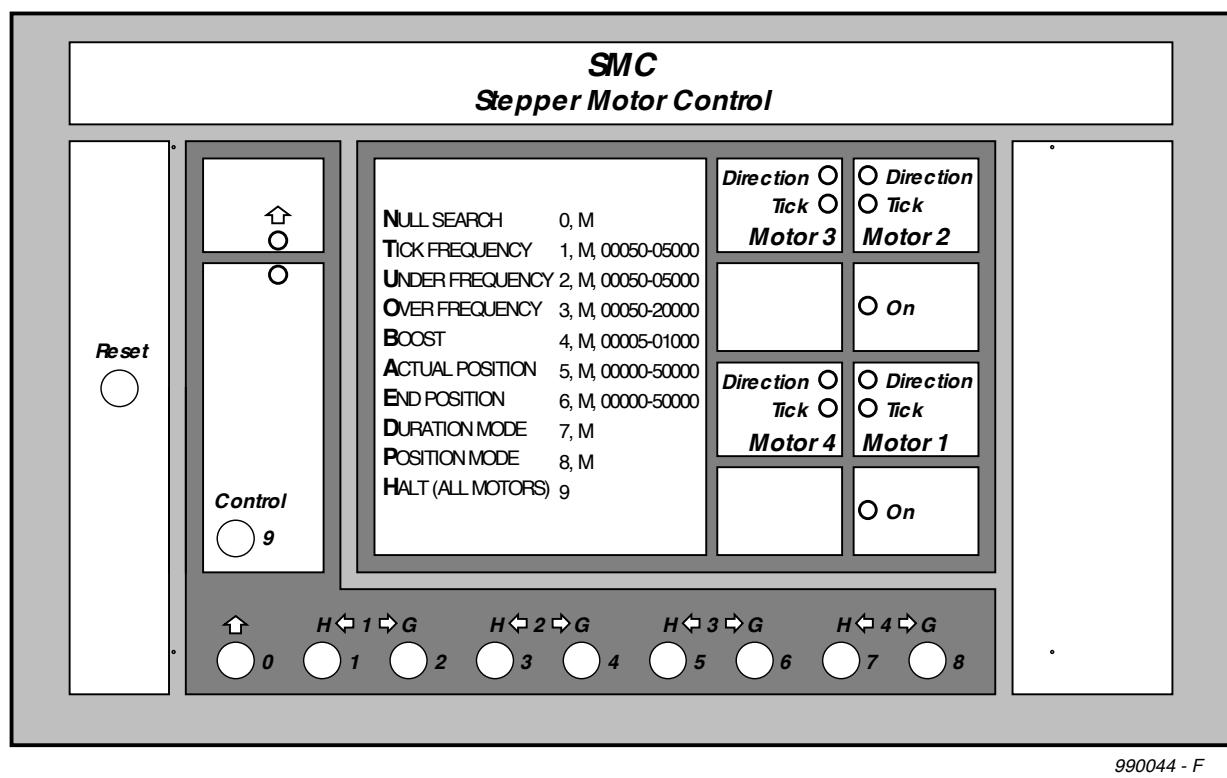

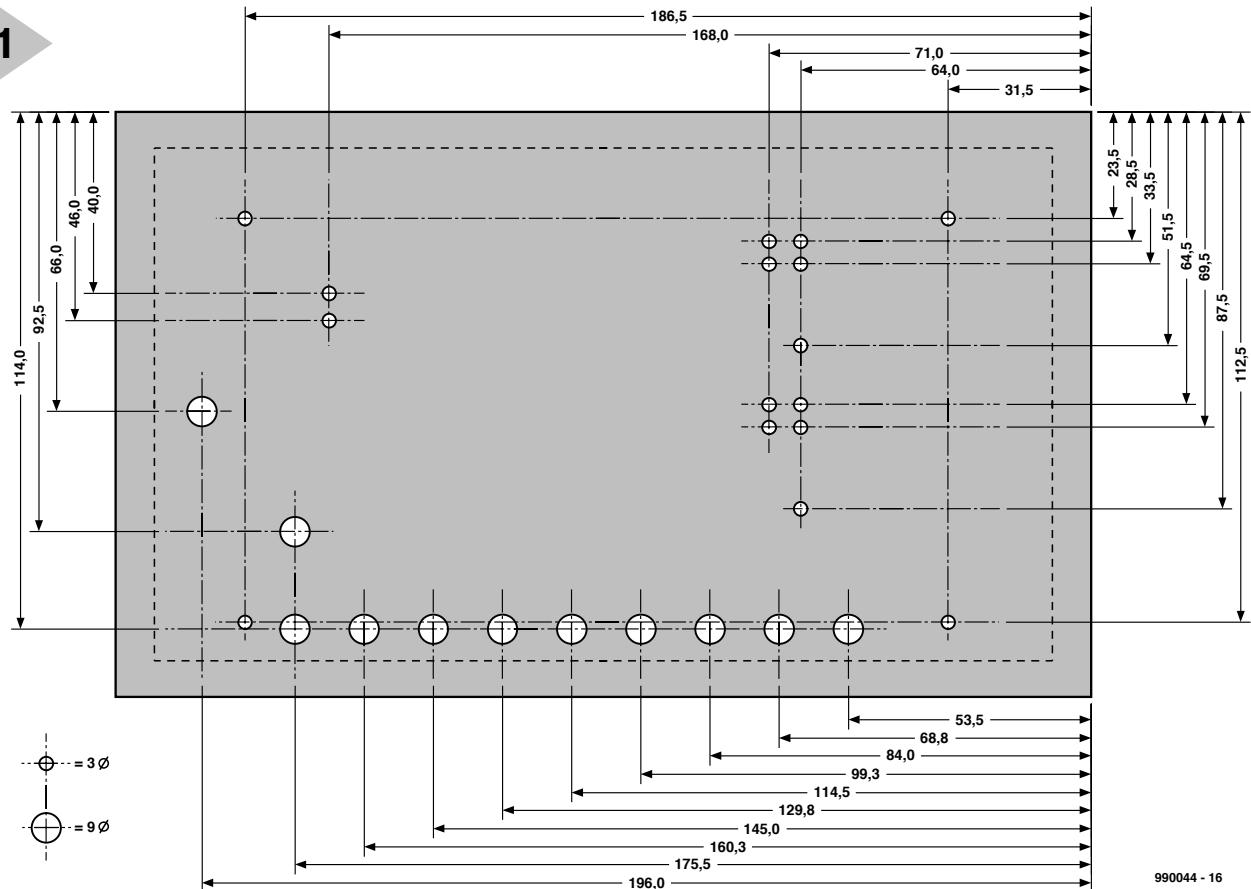

### 54 commande de moteurs pas à pas C166

**Partie 2 : mettre en marche et c'est parti !**

Nous nous intéressons dans cet article à la réalisation et la programmation de SMC.

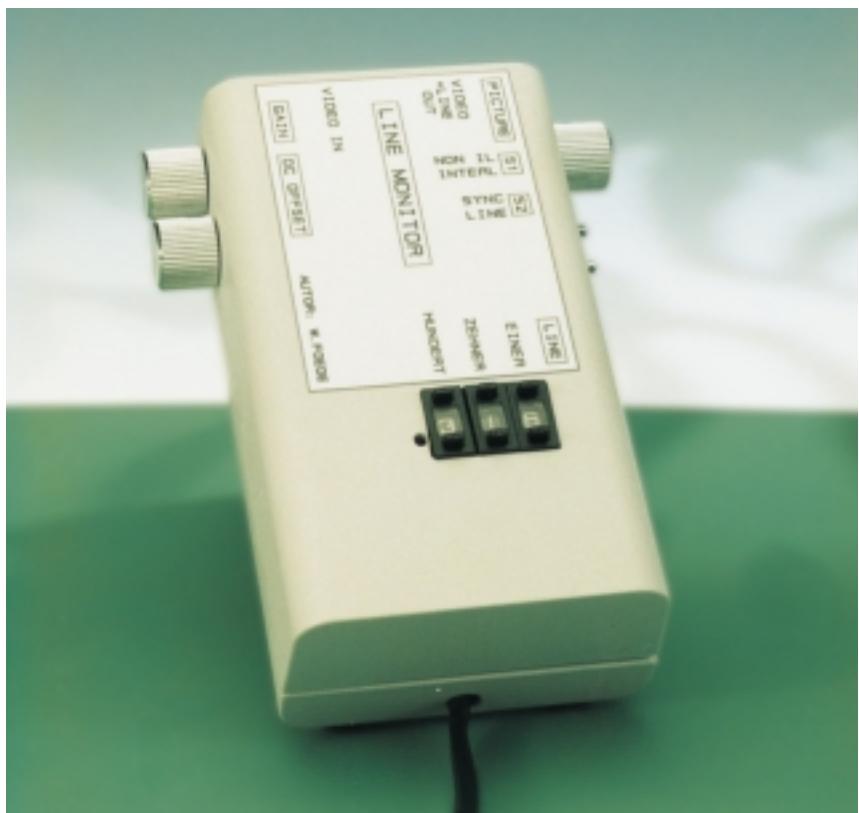

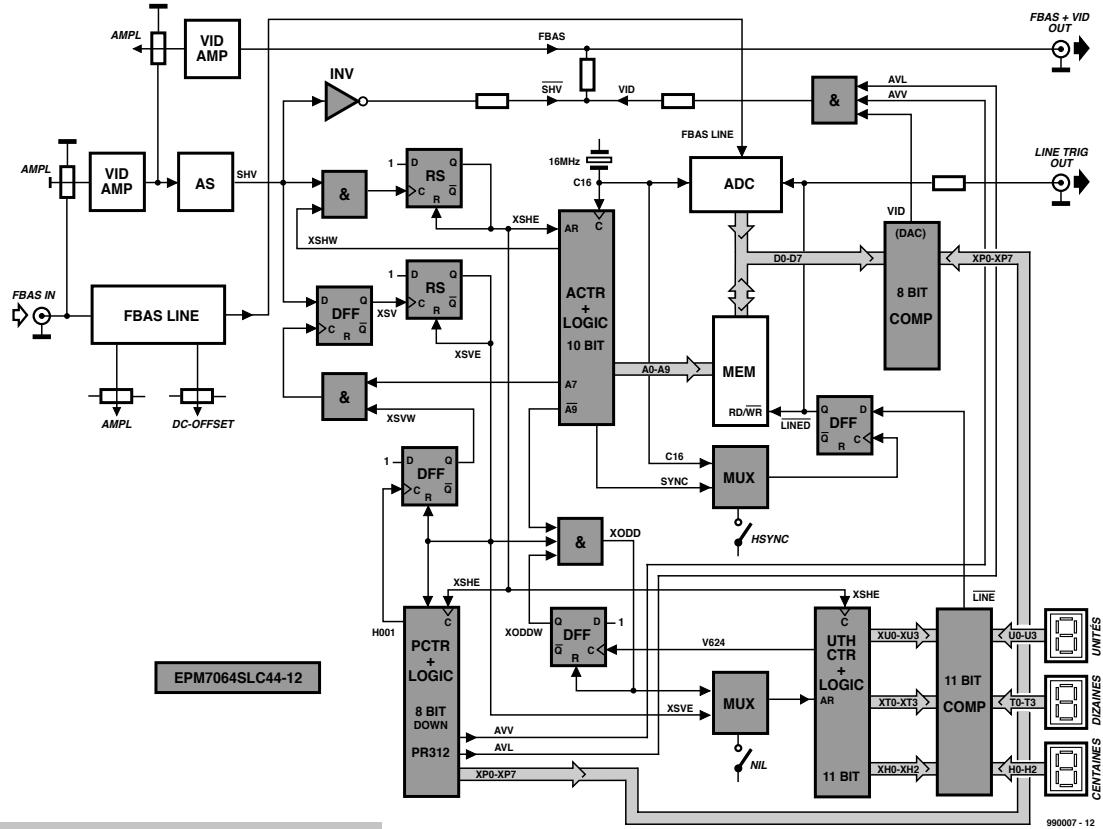

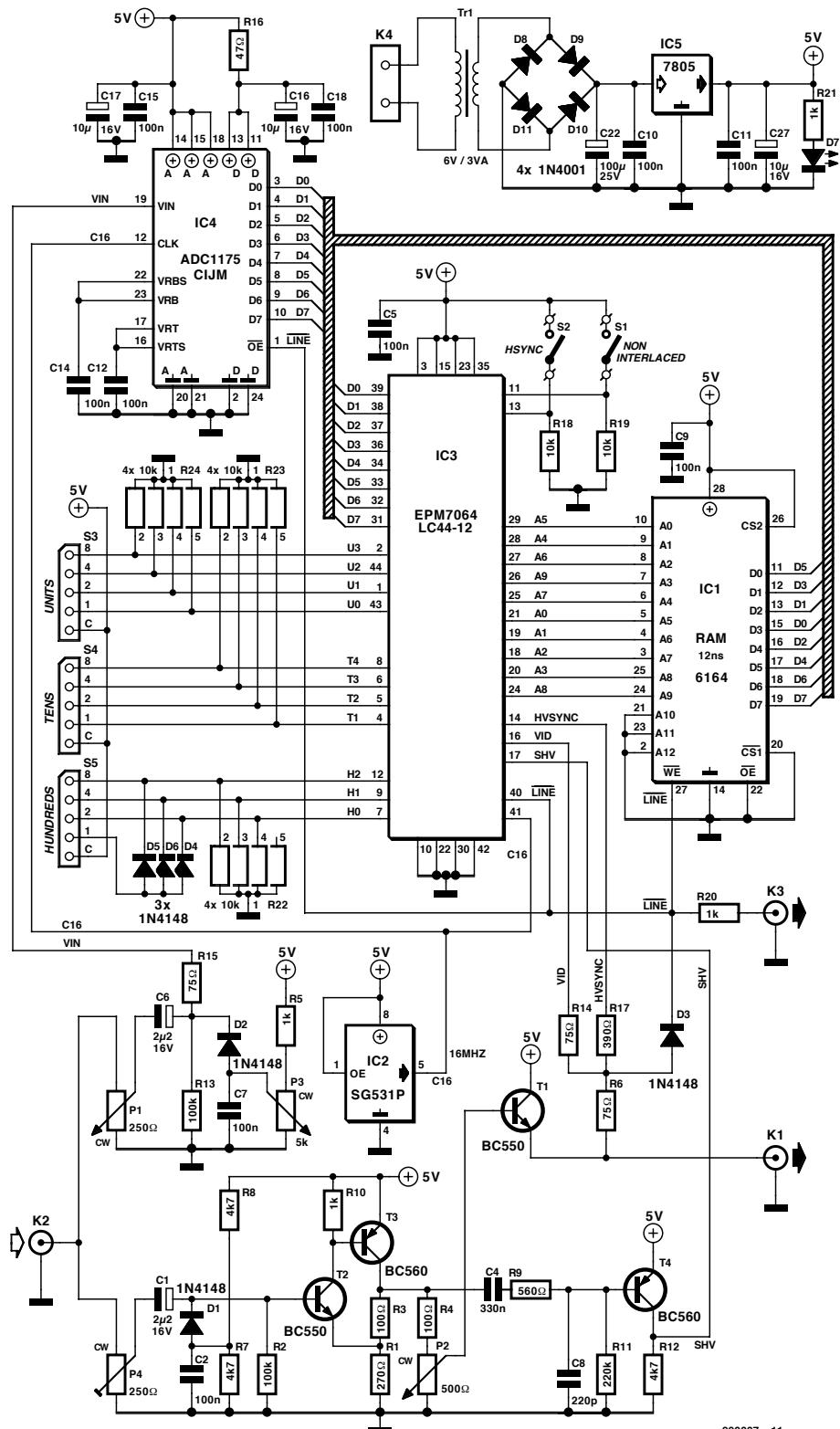

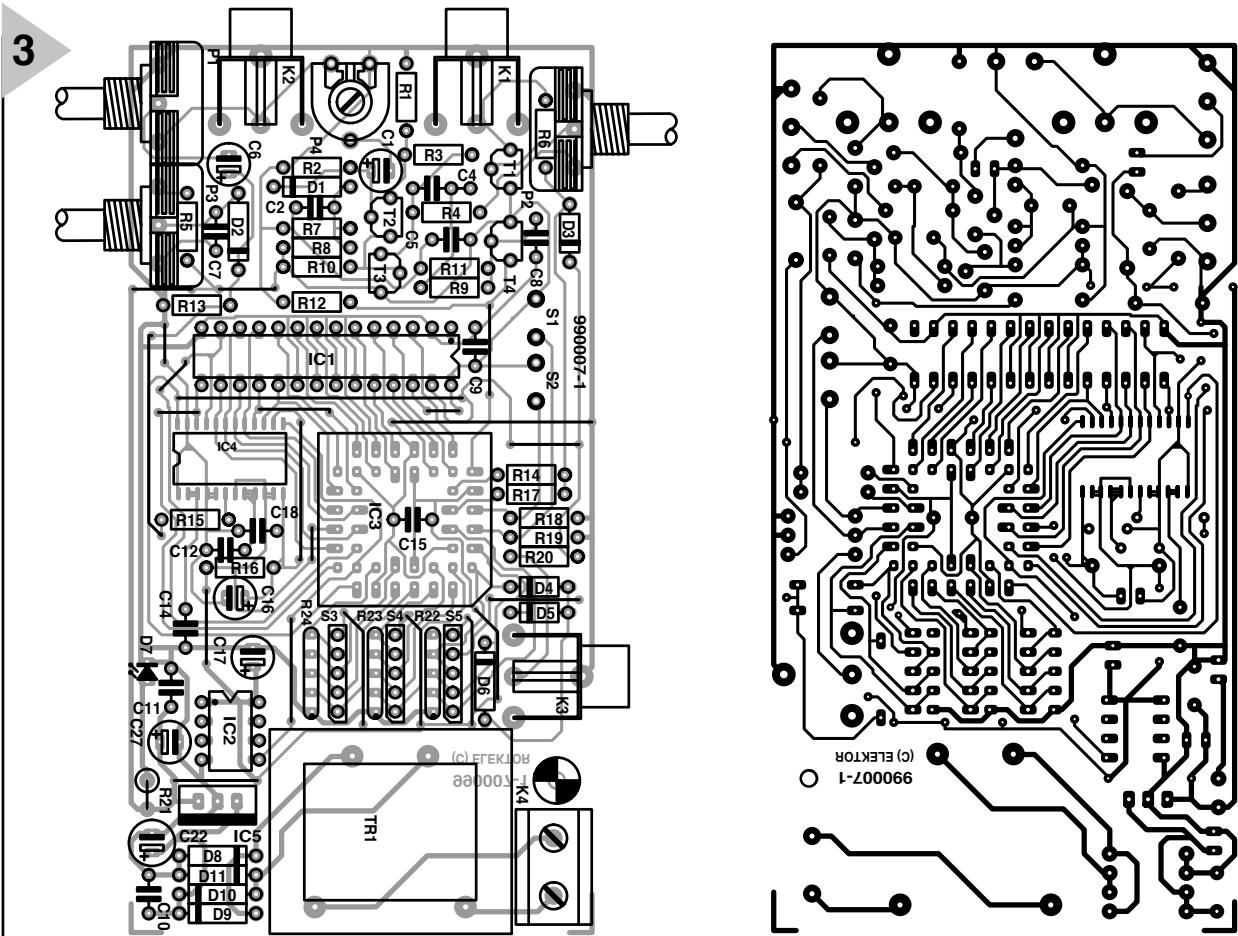

### 64 moniteur de ligne TV

sélection et contrôle de signaux vidéo

Cet appareil étonnant marque la ligne sélectionnée dans le signal de synchronisation de chrominance et l'affiche sous forme d'oscillogramme sur l'écran TV.

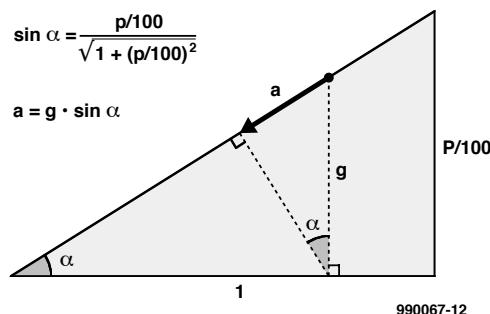

### 70 inclinomètre à base du nouveau ADXL105

Réalisez cet instrument si vous voulez connaître la pente exacte de la Dune du Pilat.

## RUBRIQUES

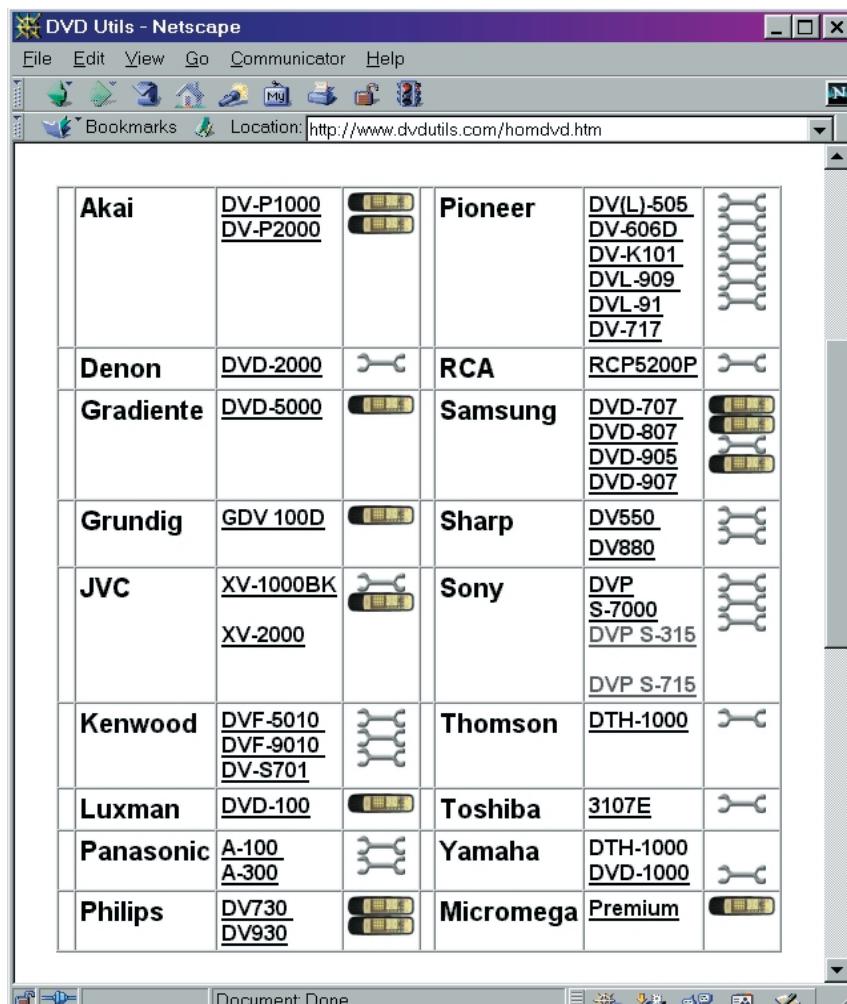

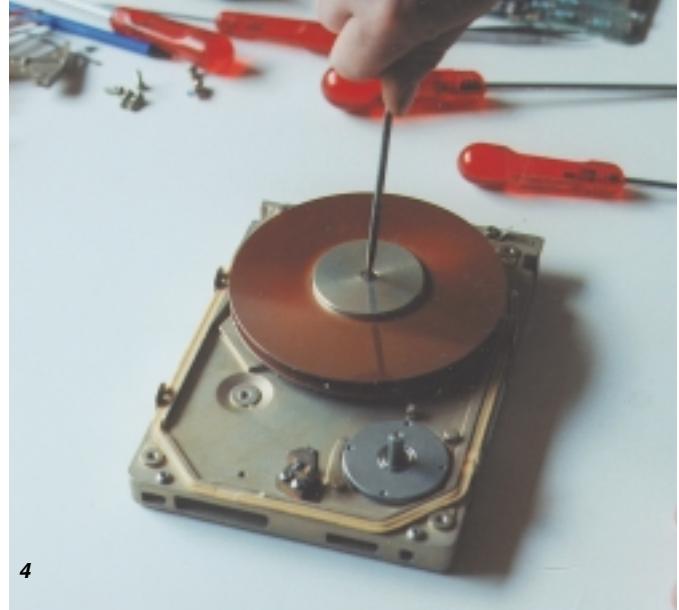

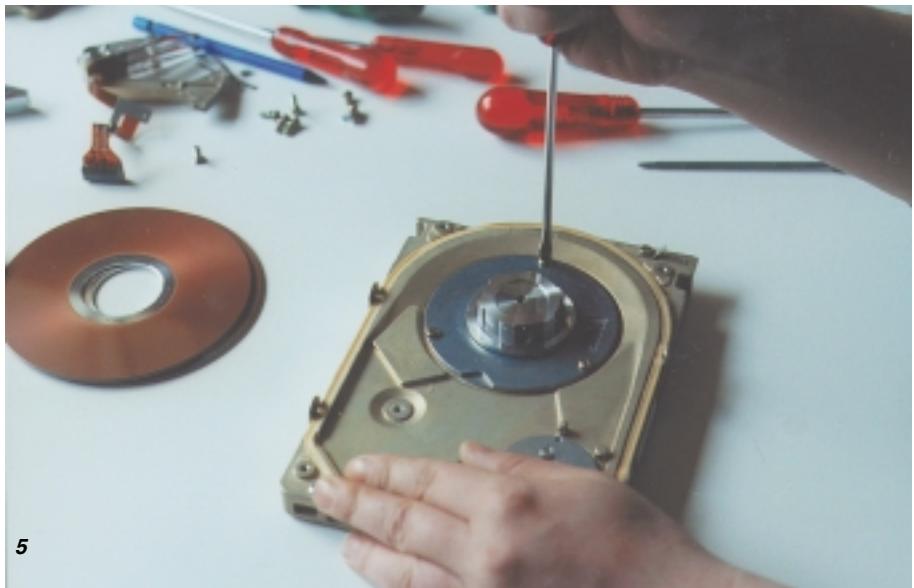

### 53 électronique en ligne modification de lecteurs DVD

### 69 Petites Annonces Gratuites Elektor

### 73 Infocartes : CS8414

### 75 CEM la réglementation de la Compatibilité ElectroMagnétique

### 82 Publitronic Service

### 84 Avant-Première

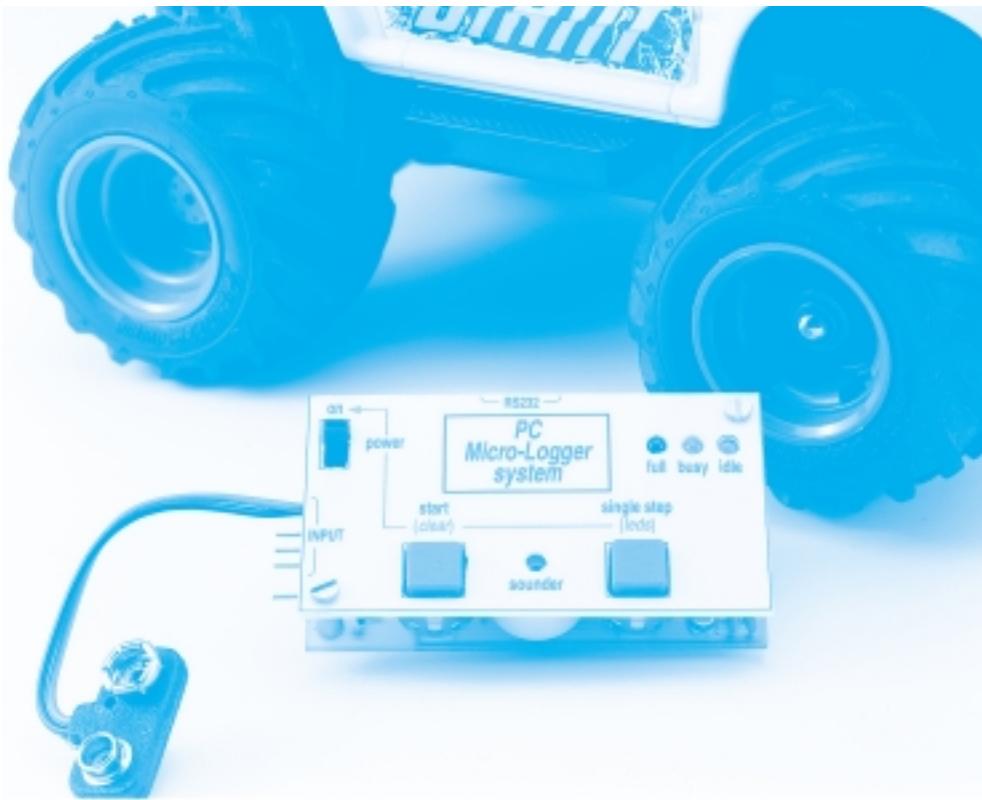

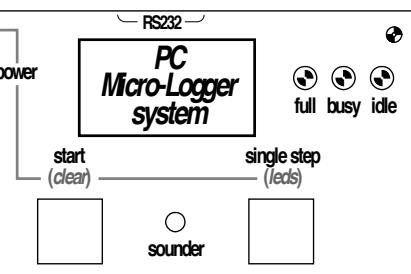

## CE MOIS-CI DANS PC-PLUS:

- Micrologger

- recyclons les moteurs des disques durs

- le tort d'Elektor

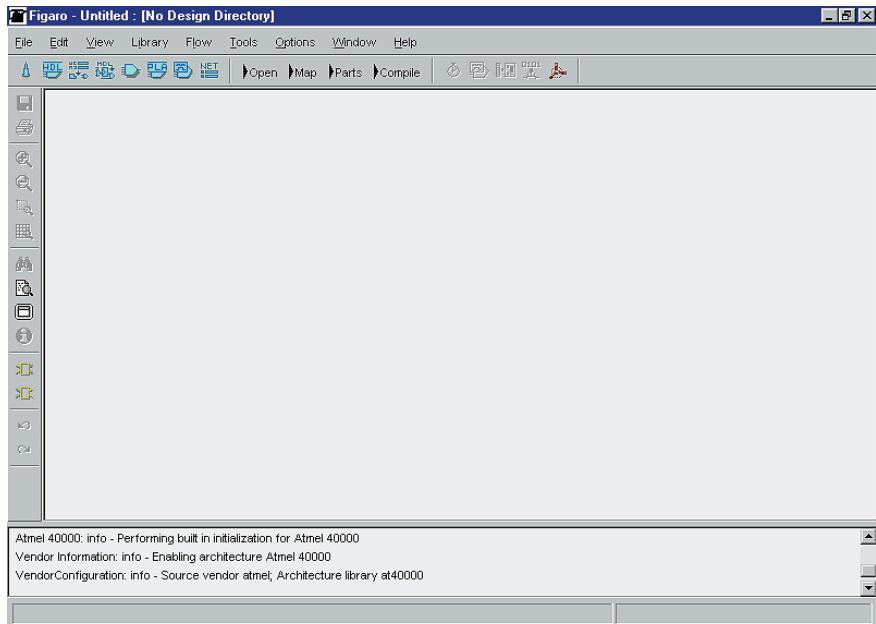

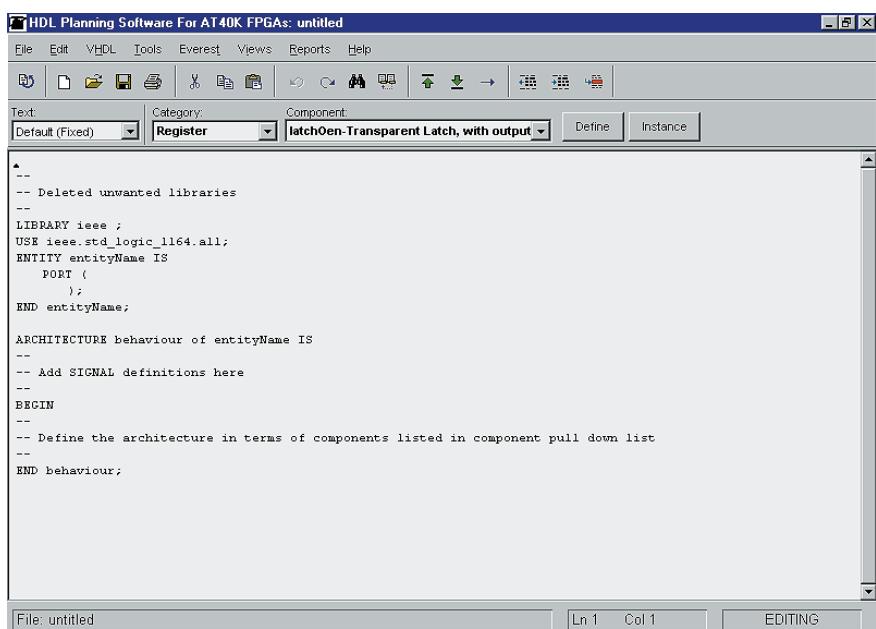

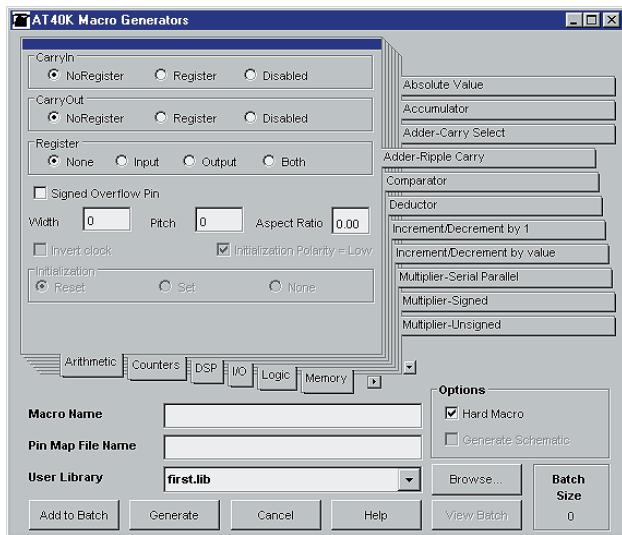

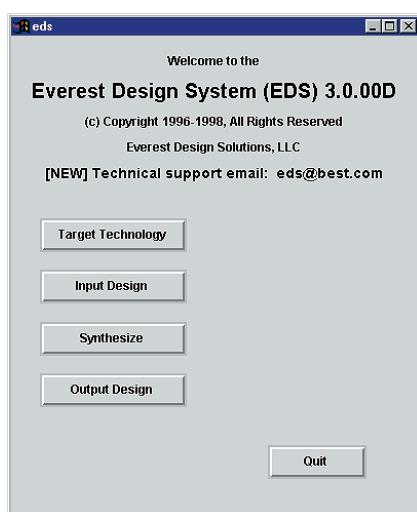

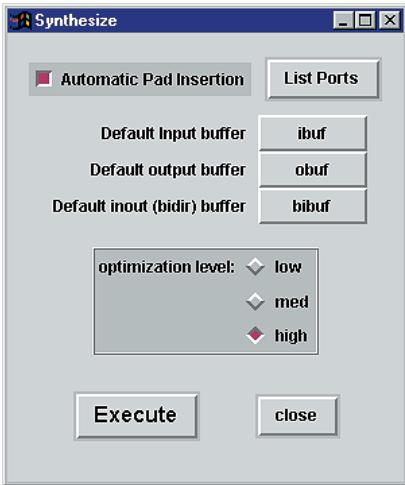

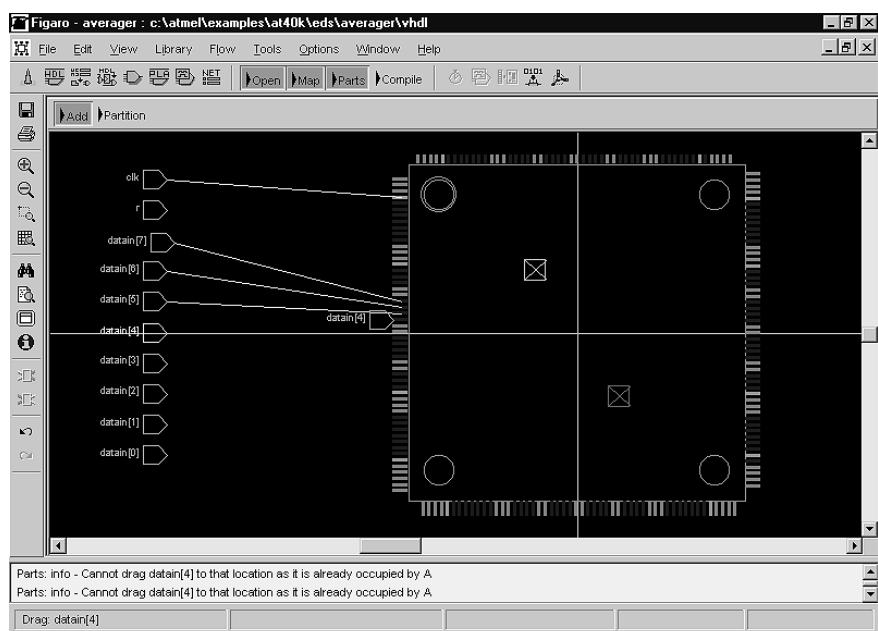

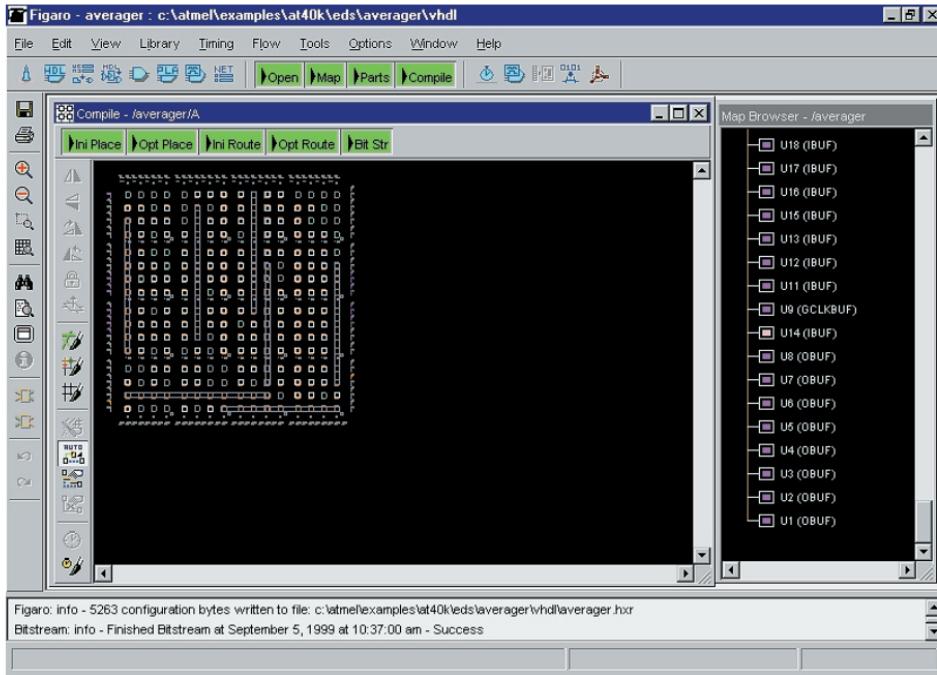

- cours : dessin de FPGA Atmel (2)

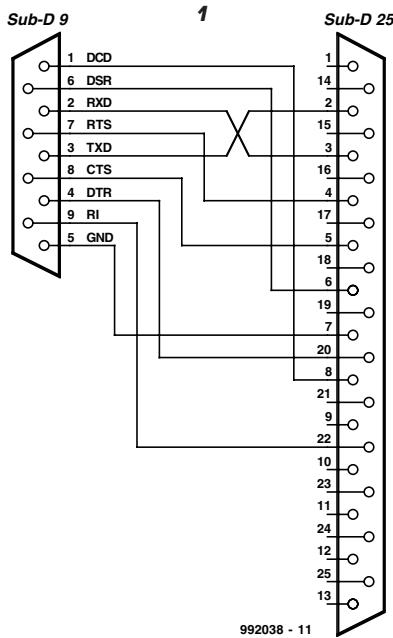

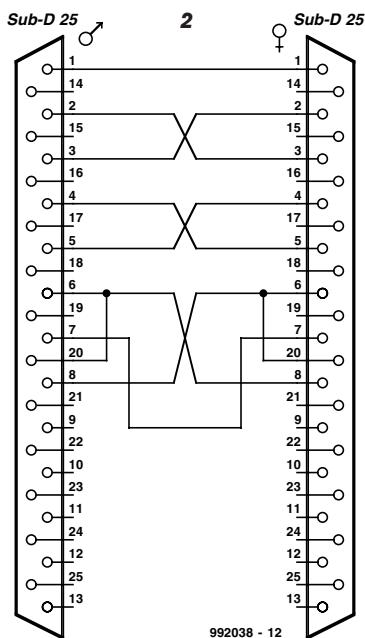

- câble à tout faire

# audio-DAC 2000 (I)

*convertisseur N/A

pour l'amateur perfectionniste*

Ce convertisseur N/A dernier-cri a été spécialement conçu à l'intention de ceux d'entre nos lecteurs qui tiennent à ce que leur installation audio soit, à l'aube de l'an 2000, à la pointe de la technologie. Sa résolution de 24 bits et sa fréquence d'échantillonnage de 96 kHz, permettent à l'audio-DAC 2000 de profiter au maximum des qualités des CD et DVD les plus modernes.

S'il est un domaine où les développements se sont succédés à une vitesse vertigineuse, c'est bien celui de l'audio numérique. Nombre d'audiophiles, tatillons quant à la qualité, ont certains doutes à ce sujet. Ils applaudissent le gain de qualité mais se refusent à suivre des développements qui ont pour conséquence des modifications incessantes de leur installation et ce, à un coût non négligeable. Il n'est pas étonnant partant que les convertisseurs N/A (CNA) décrits en 92 et 94 dans Elektor aient joui (et jouissent) encore d'une grande popularité.

Il est toujours plus simple et meilleur marché, lorsqu'il faut mettre une source audio au goût du jour, de ne remplacer que le CNA et non pas l'appareil complet. Un CNA audio autonome présente l'avantage additionnel d'être universel et, partant, de pouvoir être combiné à n'importe quel lecteur de CD/DVD ou lecteur/enregistreur numérique.

L'« audio-DAC 2000 » décrit dans le présent article peut être considéré comme étant le nec plus ultra. Avec sa résolution de 24 bits et sa capacité de travailler à toute fréquence d'échantillonnage comprise entre 32 et 96 kHz, il s'agit d'une réalisation de premier ordre, sachant que nous avons, lors de sa conception, opté pour une qualité sans le moindre compromis. Le seul petit reproche que l'on puisse faire est qu'il n'est pas prévu pour les fréquences d'échantillonnage supérieures à 96 kHz.

Permettez-nous d'y répondre par une question : utilisera-t-on jamais des fréquences plus élevées ? Le nouveau standard de 192 kHz existe bien sur papier, mais ni le matériel ni le logiciel ne se trouvent sur les étagères des magasins.

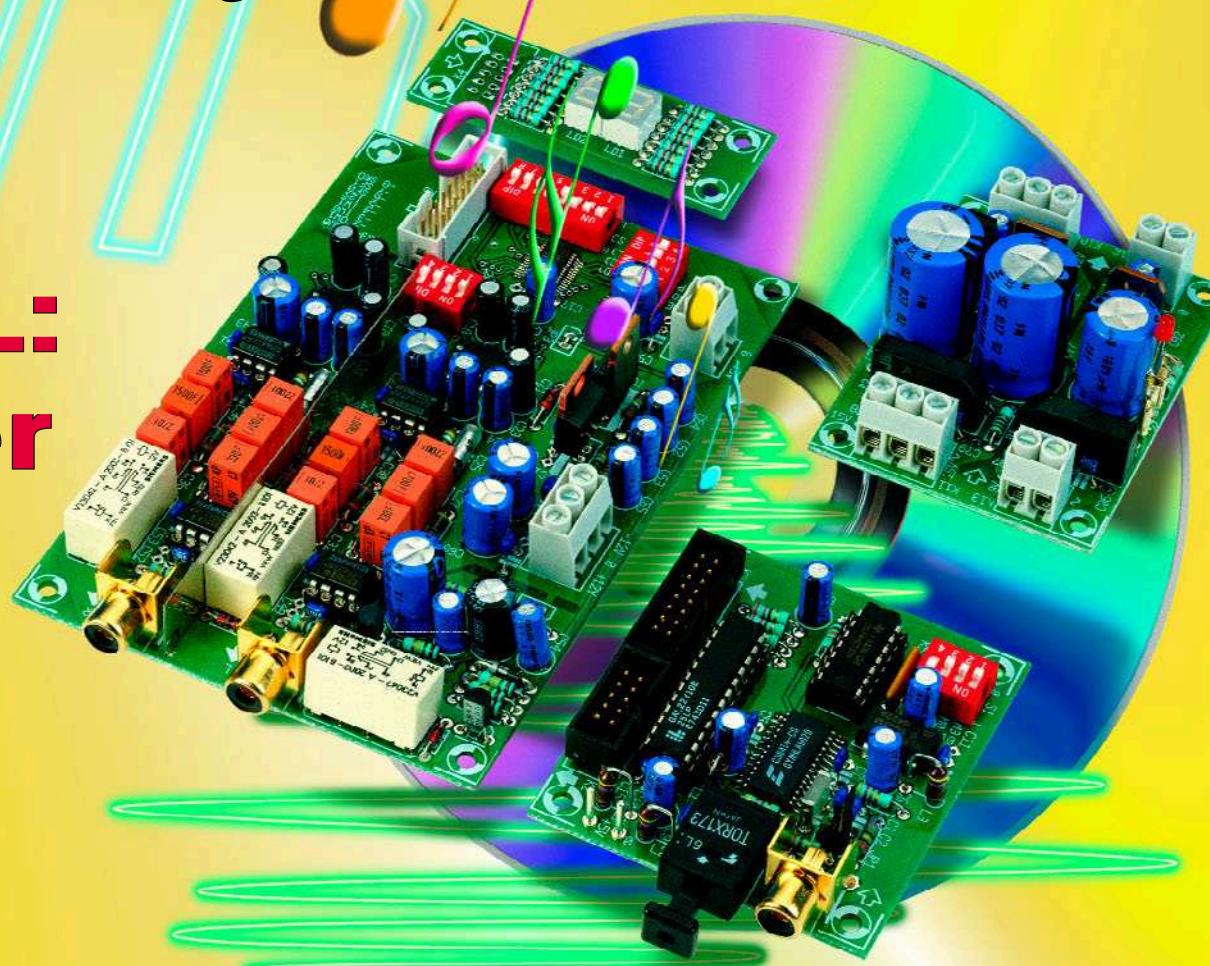

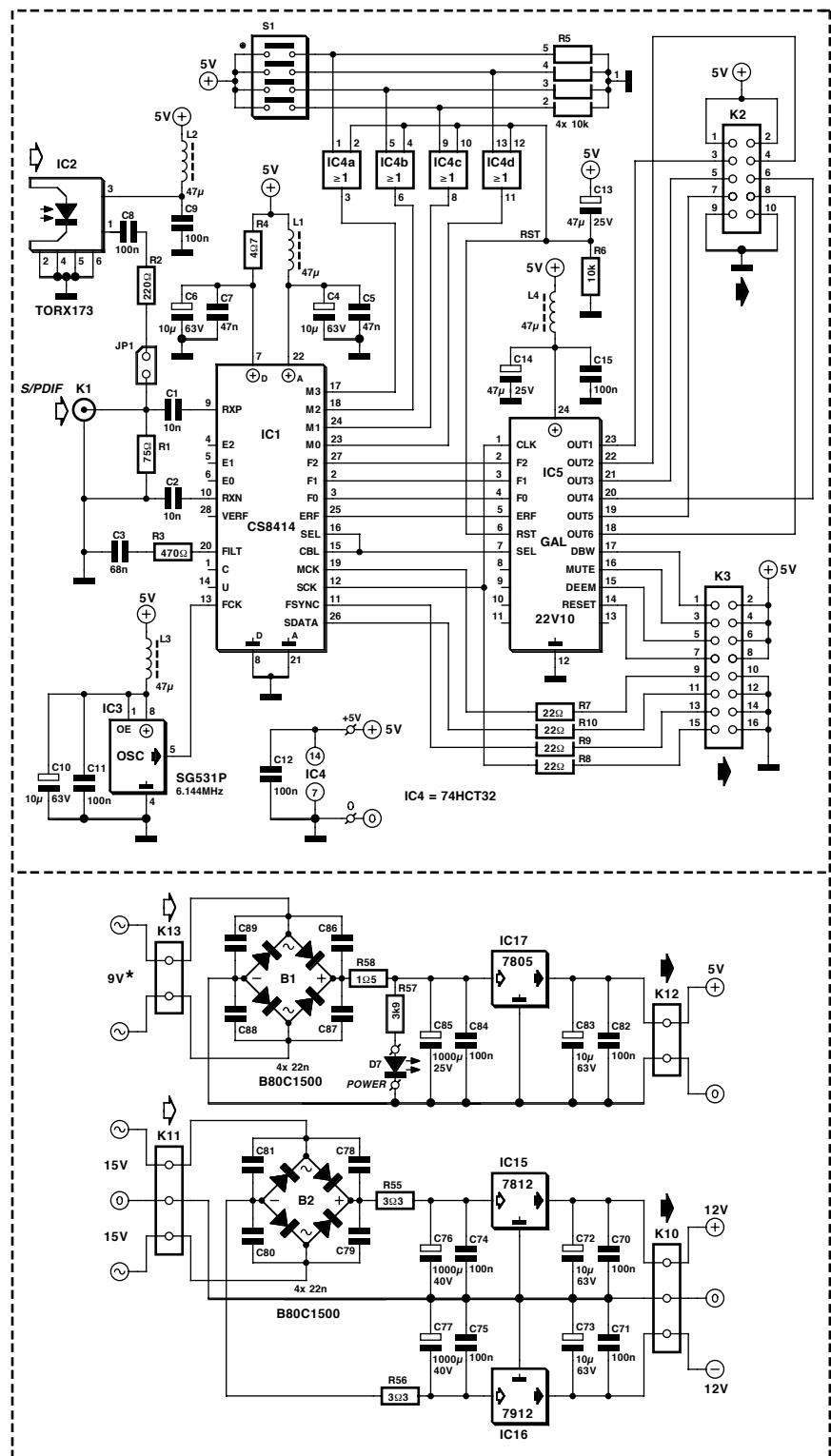

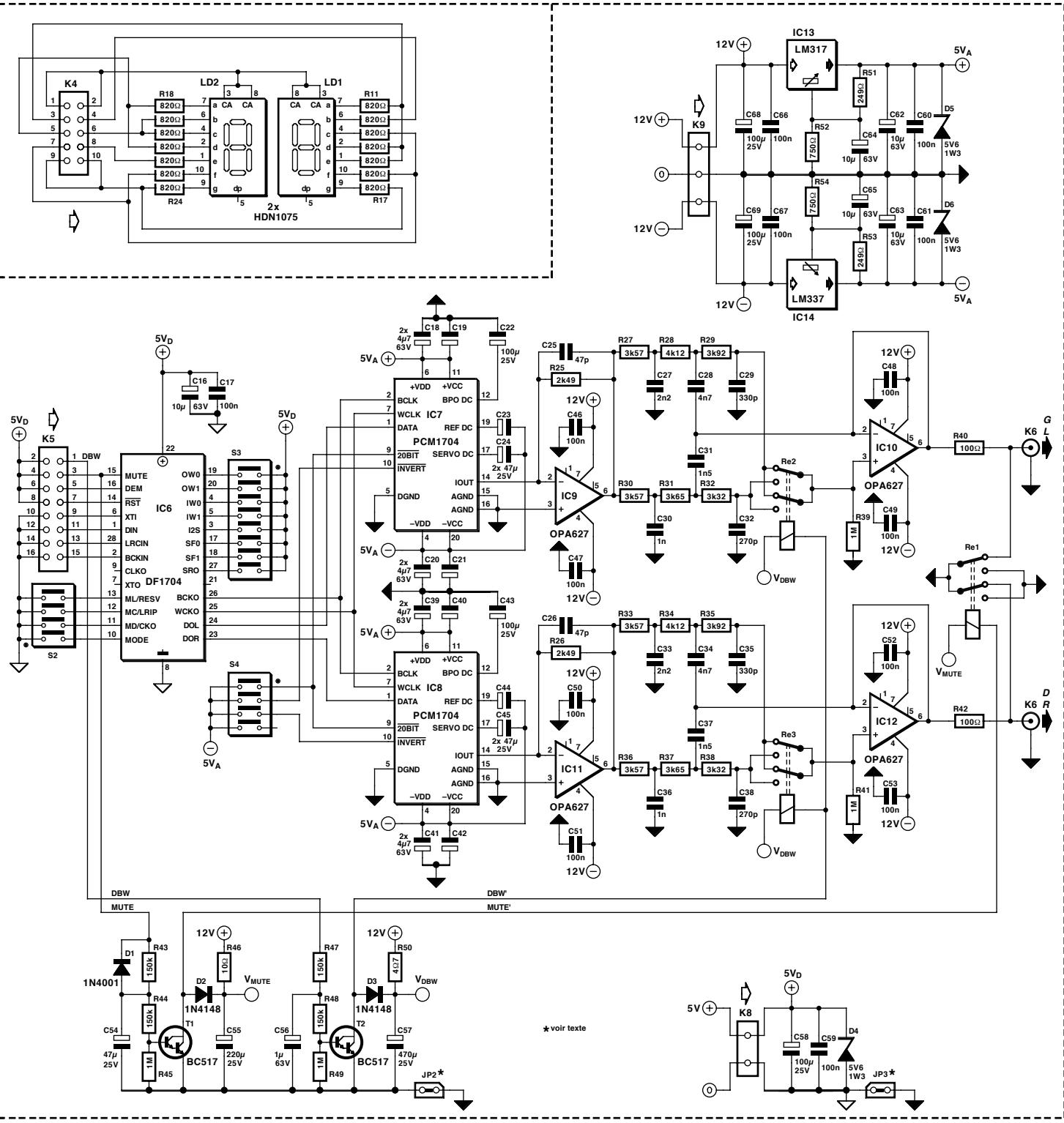

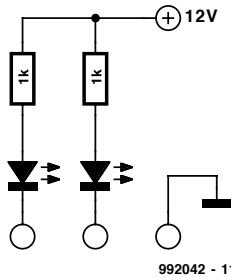

## LE CONCEPT

Le montage prend place sur 3 platines principales : l'une pour l'alimentation de  $\pm 12$  et  $+5$  V, la seconde pour le récepteur audio avec pilote d'affichage (qui, avec ses 2 chiffres, se trouve sur une quatrième platine, minuscule celle-ci) et la platine du convertisseur numérique/analogique (CNA) sur laquelle on trouve le filtre numérique, le CNA proprement dit et la section de sortie analogique.

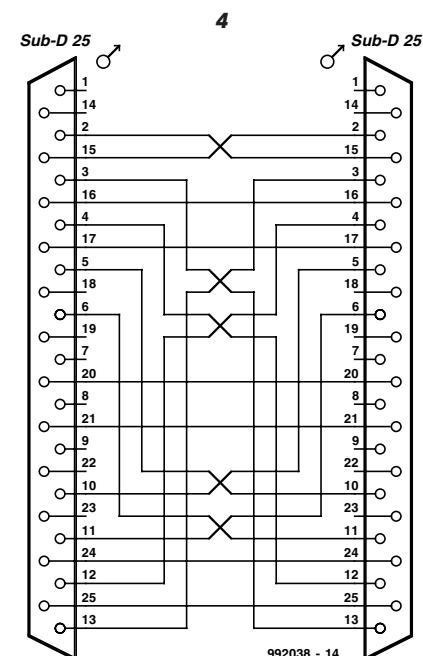

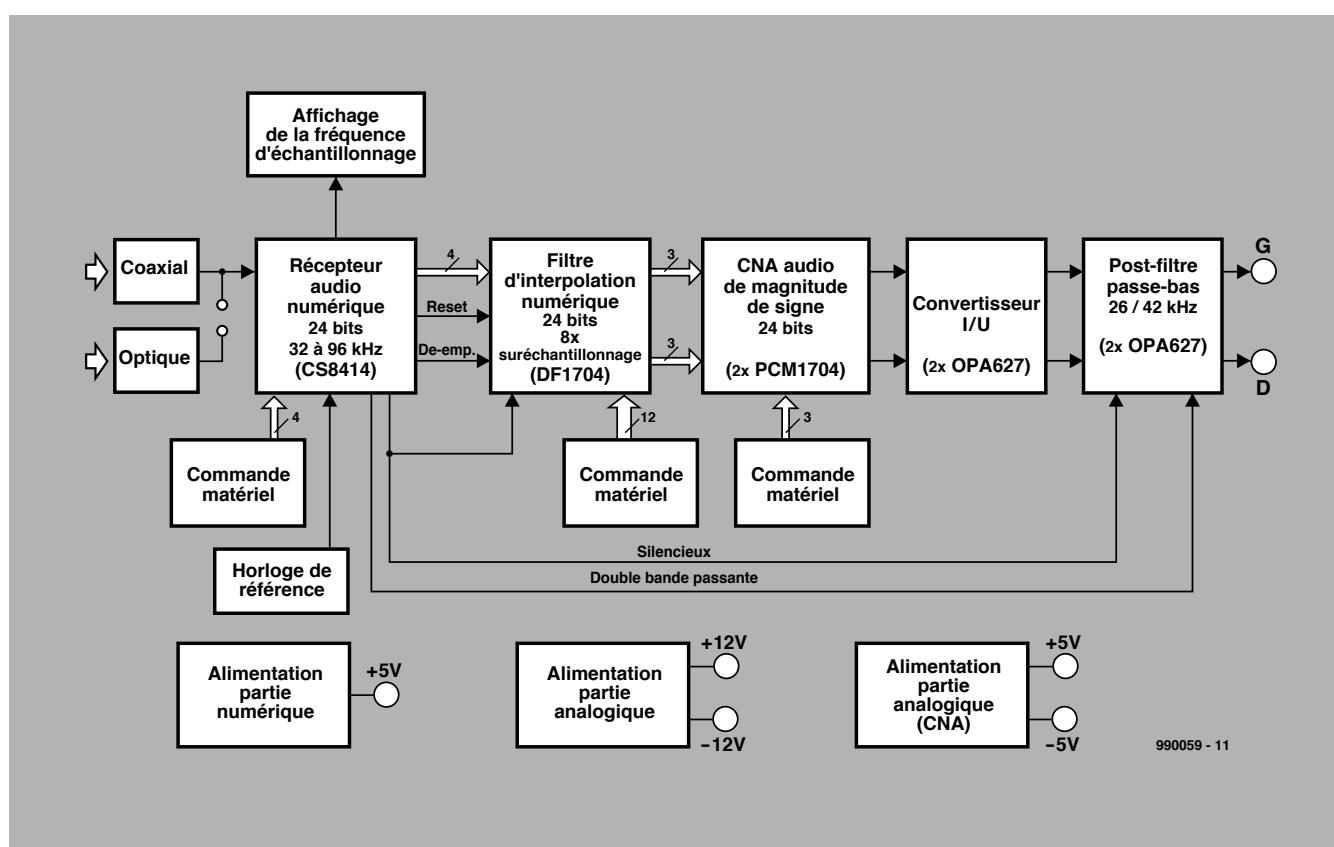

Nous vous proposons, pour expliciter la structure du montage, son synoptique en **figure 1**. On y retrouve toutes les fonctions les plus importantes. Passons en revue les différents blocs qui le constituent.

L'alimentation (en bas à gauche) comporte une partie 5 V destinée à l'alimentation des composants numériques (platine du récepteur et filtre numérique sur la platine du CNA), une alimentation  $\pm 12$  V pour les étages de sortie analogiques avec circuit à relais, ainsi qu'une tension symétrique additionnelle de  $\pm 5$  V dérivée de l'alimentation  $\pm 12$  V et destinée aux seuls convertisseurs N/A.

Le bloc « Récepteur audio numérique » s'entoure d'un affichage, d'une commande matériel et d'une horloge de référence. L'affichage comporte une paire d'afficheurs 7 segments à LED chargés de visualiser la fréquence d'échantillonnage, à savoir 32, 44, 48, 88 ou 96 kHz (44 et 88 sont en fait 44,1 et 88,2 kHz). Le bloc « commande matériel » symbolise une électronique permettant, par le biais d'un quadruple interrupteur DIP, de définir le mode de fonctionnement du récepteur (CS8414 de Crystal Semiconductor), point auquel nous reviendrons. « L'horloge de référence » est un oscillateur à quartz précis travaillant à 6,144 MHz et utilisé par un comparateur de fréquence intégré dans le CS8414 pour déterminer la fréquence de l'horloge reçue (PLL). On procède, au cœur du CS8414, à un multiplexage de la donnée indiquant la fréquence d'échantillonnage et des bits d'état de canal (*channel status*) les plus importants reçus. On n'utilise en fait, de tous les bits du canal d'état, que le bit de désaccentuation (*de-emphasis*). Il est fait appel, pour le démultiplexage des données et également, entre autres, la commande de l'affichage, à une GAL du type 22V10. En ce qui concerne les données multiplexées, celles-ci sont converties et transmises aux sorties du registre. On évite ainsi la création de

**Figure 1.** On voit, sur ce synoptique, les différents sous-ensembles fonctionnels constituant notre nouvel audio-DAC, l'audio-DAC 2000.

990059 - 11

lignes de commutation supplémentaires qui ne manqueraient pas, au niveau d'un affichage multiplexé en particulier, de générer un niveau de parasitage très important. En mode de fonctionnement normal, toutes les sorties de la GAL sont statiques. Certaines des liaisons requises par l'affichage ont été interconnectées a priori de manière à limiter au strict nécessaire le nombre de sorties de la GAL, ce qui permet de se contenter d'une 22V10. L'interconnexion au récepteur audio se fait par le biais de 2 câbles en nappe. Un câble plat à 10 conducteurs relie la platine de l'affichage au récepteur.

Un second câble en nappe, à 16 conducteurs cette fois, interconnecte la platine du récepteur à celle du CNA; il sert également au transfert d'un certain nombre de signaux en direction du filtre numérique, un DF1704 de Burr-Brown. Il s'agit de la tension d'alimentation de 5 V, du signal de données audio sérielles (SAD = *Serial Audio Data*) et de 4 autres signaux importants : les signaux de remise à zéro (RAZ) à la mise sous tension (= POR pour *Power On Reset*), de désaccentuation, de silencieux (*mute*) et de commutation servant à faire passer le filtre analogique vers une bande passante double (*double bandwidth*) au cas où l'on a détection de fréquences d'échantillonnage de 88,2 ou 96 kHz. Le signal de silencieux est activé en l'absence de signal à l'entrée du récepteur ou lorsque la boucle à verrouillage de phase (PLL pour *Phase Locked Loop*) n'arrive pas à accrocher. Ce signal de silencieux, dérivé directement de la sortie d'erreur (ERF) du CS8414 sert non seulement à la désactivation du relais de sortie mais également à faire basculer le filtre numérique en mode silencieux.

L'impulsion de RAZ destinée au CS8414 et générée par le réseau RC (C13/R6) sert également, après inversion dans la GAL, à la RAZ à la mise sous tension du filtre numérique. Le signal de désaccentuation a pour fonction de permettre au filtre numérique de corriger l'accentuation que pourrait présenter le matériau-source. Une douzaine d'interrupteurs DIP permettent un paramétrage du filtre, tant au niveau des formats d'entrée et de sortie que de celui du nombre de bits, de la courbe du filtre, etc...

Le filtre numérique attaque une paire de CNA. Chaque canal comporte un CNA du type PCM1704, pour lequel le filtre numérique DF1704 constitue le complément idéal. Les CNA se laissent également paramétrier au niveau du matériel. Nous y reviendrons plus tard. Les sorties des CNA sont de pures sources de courant; nous avons opté, pour des raisons de tension parfaitement définie, de bonne linéarité, de

**Figure 2. Le schéma complet présente un emboîtement respectable. Les pointillés délimitent les différentes plaques nécessaires par cette réalisation.**

niveau de bruit faible, de tension de dérive (*offset*) faible et de taux de montée (*slew-rate*) élevé, pour un OPA627 par CNA. Il ne s'agit sans doute pas de l'amplificateur opérationnel le moins cher, mais il possède les caractéristiques requises pour cette application. Le filtre analogique pris à la sortie est requis pour éliminer, par filtrage, les résidus des produits de suréchantillonnage et de bruit HF. Il a été prévu, de

manière à pouvoir utiliser au mieux les 2 fréquences d'échantillonnage les plus élevées, une possibilité de commutation du filtre analogique entre 2 fréquences de coupure. Chaque section de filtrage comporte un relais bipolaire par fréquence de coupure vu que l'utilisation d'un unique relais pour les 2 canaux se traduirait, aux fréquences élevées, par une diaphonie (séparation des canaux) trop mauvaise (les sec-

tions RC des filtres présentent une « impédance trop élevée » pour cela. On utilise à la sortie, tant pour la fonction de silencieux que pour l'élimination des plos de mise sous tension, un relais bipolaire vu que la résistance de sortie par canal ne dépasse pas  $100\ \Omega$ .

## LE RÉCEPTEUR

Il est temps, après nous être intéressés au synoptique, de passer au détail. Utilisons pour cela le schéma représenté en **figure 2** qui rend la totalité de l'électronique constituant notre audio-

DAC 2000. L'une des sections les plus importantes du montage est celle chargée du décodage du flux de données S/PDIF pour leur donner un format serial utilisable par les CNA. C'est là la tâche de IC1, un CS8414 de Crystal. L'électronique de soutien de ce composant prend place sur une mini-platine distincte de manière à permettre un placement aisément de l'entrée coaxiale et optique sur l'arrière du boîtier voire n'importe où ailleurs. L'impédance d'entrée du récepteur est définie par R1 et prend ainsi la valeur

standard de  $75\ \Omega$  utilisée pour les liaisons coaxiales. Nous avons opté, en ce qui concerne l'entrée optique, pour une solution simple. Nous relierons la sortie d'un récepteur Toslink TORX173, IC2 (une liaison optique classique sur les appareils grand public), par le biais du diviseur de tension R1/R2 et d'un condensateur de couplage – destiné à bloquer la composante de tension continue en provenance du TORX173 – à l'entrée du CS8414. Le dimensionnement du diviseur de tension est tel que le signal aux bornes de R1 dépasse

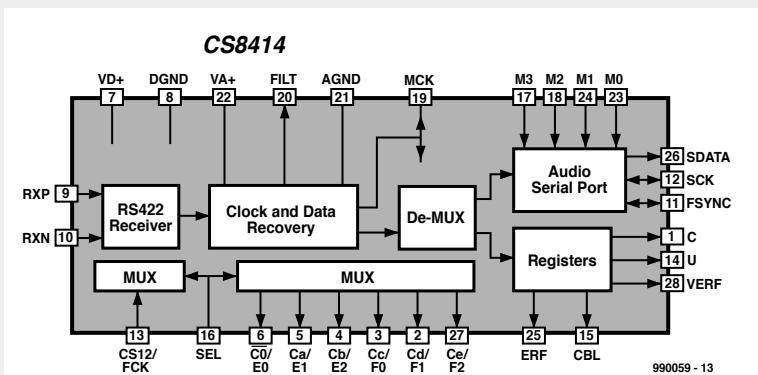

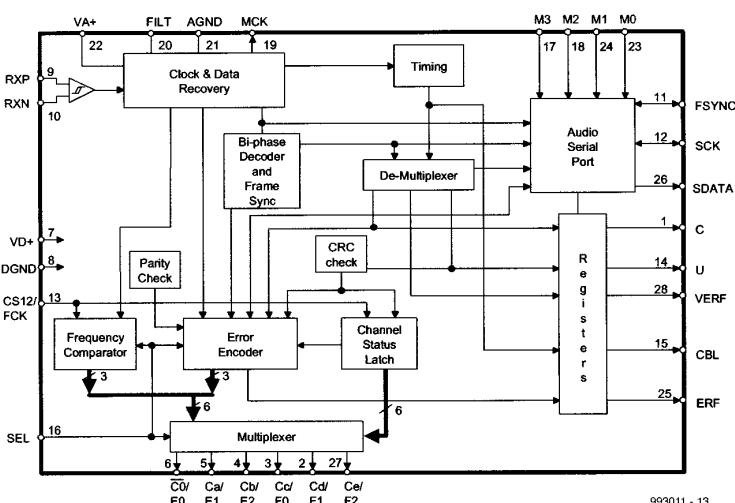

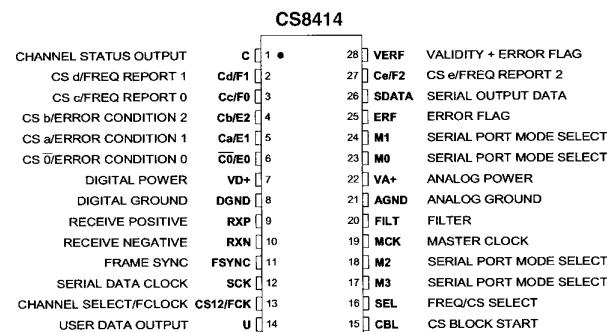

# Le CS8414

La dénomination du récepteur ne devrait pas manquer de rappeler quelque chose à la plupart d'entre nos lecteurs. Il s'agit en effet du successeur du CS8412 que nous avons utilisé dans plusieurs montages (Vu-mètre numérique, avril/mai 1996, indicateur d'écrêtage numérique, octobre 1998 et le moniteur S/PDIF de juillet/août de cette année). Le nouveau CS8414 est compatible broche à broche avec le CS8412 mais uniquement disponible en boîtier SOIC (CMS standard) à 28 broches.

L'une des différences les plus marquantes par rapport à son prédecesseur est que la plage des fréquences d'échantillonnage du CS8414 a été étendue jusqu'à 96 kHz. On a oublié l'indication de fréquence à une précision de 400 ppm du CS8412 pour pouvoir afficher les fréquences de 88,2 et 96 kHz. La détection d'horloge se fait par une PLL associée à un filtre de boucle du second ordre, dont le filtre RC externe est dimensionné différemment que dans le cas du CS8412. L'entrée du CS8414 est en fait un récepteur RS422 capable de traiter des signaux tant symétriques qu'asymétriques. Dans le cas présent, l'entrée est configurée pour des signaux asymétriques (single ended), l'entrée RXN étant découplée vers la masse. L'entrée comporte un trigger de Schmitt de 50 mV pour permettre un fonctionnement optimal du détecteur de phase de la PLL interne.

légèrement, avec ses quelque 0,6 V, les 0,5 V qui sont le standard d'un signal coaxial. Il faut planter un cavalier, JP1, pour pouvoir utiliser l'entrée optique; il est interdit alors de connecter une source coaxiale. Il est bien prévu une possibilité d'utiliser, tout en utilisant l'entrée optique, l'entrée coaxiale en tant que sortie S/PDIF (convertisseur optique/coaxial). Dans ce cas-là, l'impédance de sortie et le niveau du signal ne respectent pas les normes, mais il est possible, en diminuant quelque peu la valeur de R2, de rehausser légèrement le niveau du signal. Le signal d'entrée du CS8414 peut même dépasser, de 0,3 V, le niveau de la tension d'alimentation; 1 Vcc aux bornes de R1 ne pose donc pas de problème.

Le circuit intégré comporte plusieurs détecteurs de fréquence en vue de permettre le verrouillage le plus rapide possible de la PLL sur le flux de données entrant. En l'absence de signal d'entrée, la fréquence du VCO (*Voltage Controlled Oscillator* = oscillateur commandé en tension) est minimale.

Le filtre numérique présent sur la platine du CNA requiert 4 signaux, fournis tous les 4 par le CS8414 qui les distille des données S/PDIF d'entrée. SDATA représente bien entendu les

à M3 sont un peu dans le désordre, mais elles sont indiquées clairement sur la platine de même que le niveau ON ou OFF.

Les autres formats sont souvent justifiés à droite, bit de poids fort (MSB = *Most Significant Bit*) en premier (« MSB-first right-justified » dit l'anglais) ce qui signifie que la position du bit de poids faible est fixée par rapport à l'horloge G/D, ce qui veut dire qu'il existe, pour un certain nombre d'octets, un risque de perte de l'un ou l'autre MSB. Dans le mode I<sup>2</sup>S, la position du bit de poids fort est fixée et partant, pour un nombre de bits plus important, seuls quelques bits de poids faible (LSB = *Least Significant Bit*) se trouvent à 0. On n'a pas ainsi de mutilation des signaux. Certains des autres formats disponibles sont compatibles avec le filtre numérique de Burr-Brown mais sont en fait réservés aux amateurs d'expériences. C'est à dessein qu'il a été prévu une possibilité de paramétrage des différents modes en vue d'extensions/réactualisations ultérieures, voire d'autres applications. Cela permet également d'utiliser la platine du récepteur avec d'autres audio-DAC. C'est à cet effet que la platine a été dotée d'une borne pour la tension d'alimentation de 5 V vu que le 5 V arrive également par le biais de l'embase K3 (en provenance de la platine du CNA).

Le fabricant recommande une RAZ du circuit intégré dès après la mise sous tension, d'où la présence d'une électronique à base de 4 portes OU, IC4. Ce circuit n'a pas été intégré dans la GAL sachant qu'il aurait exigé 4 entrées et sorties additionnelles. Le circuit intégré est remis à zéro lorsque toutes les broches de mode sont forcées au niveau haut, ce qui explique que l'interrupteur DIP attaque l'entrée mode au travers des portes OU. C'est le réseau RC R6/C13 qui produit la RAZ, ce réseau assurant également, par le biais de la GAL, une RAZ du filtre numérique présent sur la platine du CNA.

Le CS8414 a besoin d'une fréquence de référence précise de 6,144 MHz pour déterminer la fréquence d'échantillonnage. C'est un oscillateur à quartz, IC3, une version miniature du SG531P, qui la fournit, la sortie de ce composant devant se trouver le plus près possible de l'entrée de IC1 correspondante, FCK, en vue de minimiser le niveau de parasitage de ce signal d'horloge. Il faut en outre veiller à un découplage efficace de l'alimentation, ce qui est ici l'affaire de L3/C10/C11. Les autres circuits intégrés sont eux aussi dotés de leur propre découplage d'alimentation. Les lignes d'alimentation de IC1, tant analogique que numérique, ont leur propre découplage. Ni la sortie C de l'état de canal, ni la sortie U du bit utilisateur (*User bit*) ni l'indicateur de validité + erreur VERF (*Validity + Error*)

*Flag*) ne sont utilisés. On fait appel au signal CBL (*Channel Status Block*) pour le démultiplexage des bits de la sortie du Channel Status (broches 2 à 6 et 27) par leur interconnexion à la broche de sélection (SEL). Si SEL présente un niveau bas on place les bits de condition d'erreur (*Error Condition*, sans objet ici) et de signalisation de fréquence (*Frequency Reporting*) aux sorties, à savoir E0 à E2 et F0 à F2. Si SEL est haut, on a application, aux sorties correspondantes, de l'état de canal sous la forme de quelques bits de l'état de canal (les sorties s'appellent alors C0, C1 à Ce). Seul Cc (F0), qui est le bit C3 de l'état de canal, est utilisé. En d'autres termes : il s'agit du bit d'accentuation de l'état de canal. La GAL en effectue une inversion et un stockage par le biais d'une sortie de registre, de sorte qu'elle garde le niveau actuel et ne suive pas SEL dans ses commutations. D'où l'interconnexion de la sortie CBL avec une entrée de la GAL dans le but de démultiplexer l'information.

Si SEL présente un niveau bas, les bits de fréquence F0 à F2 sont décodés vers 6 sorties de registre en vue du pilotage

d'un affichage à 2 afficheurs à LED. Par la combinaison, à priori, de quelques-uns des segments de l'affichage, on n'a besoin, pour la paire d'afficheurs 7 segments à LED, sans avoir à multiplexer, que de 6 sorties pour obtenir la visualisation de 5 fréquences d'échantillonnage. Nous avons cependant dû oublier le chiffre après la virgule (la fréquence est affichée en kHz). Les 6 sorties, le + 5 V et la masse sont transmises, par le biais de K2, d'un morceau de câble en nappe à 10 conducteurs et de K4, vers la platine de l'affichage. Nous n'avons pas prévu d'embase sur la platine de l'affichage pour éviter des problèmes lors de son positionnement derrière la face avant. Si la ligne ERF est active, toutes les sorties de l'affichage passent au niveau haut ce qui se traduit par l'allumage des segments centraux des afficheurs. Les 2 segments g des afficheurs sont, par le biais de R17 et R24, reliés directement à la masse et restent allumés, du moins tant que le montage est sous tension. Le cadencement des toutes les sorties de registre se fait par le biais de l'horloge SCK (vers la broche 1 de la GAL). L'information concernant la fréquence

d'échantillonnage actuelle sert, non seulement au pilotage de l'affichage de la fréquence mais aussi à la commutation du filtre de sortie analogique vers une fréquence de coupure plus élevée. La sortie DBW (*Double BandWith*) passe donc au niveau haut en cas de détection d'une fréquence d'échantillonnage de 88,2 ou 96 kHz. La sortie de désaccentuation (*Deem*) attaque uniquement le filtre numérique –nous n'avons pas prévu de signalisation à ce niveau sachant qu'avec les CD, l'accentuation est devenue rare. Cependant, comme le filtre numérique disposait de cette fonction nous l'avons mise à profit pour la correction d'une éventuelle accentuation d'autant plus que cela ne nécessitait pas de combinaison RC additionnelle, par canal, dans le filtre de sortie analogique.

990059-1

*Nous voici arrivés à la fin du premier article consacré à l'audio-DAC 2000. Le mois prochain nous vous proposerons la description de la platine du CNA et nous intéresserons plus particulièrement, et de plus près, au filtre numérique DF1704 et des CNA PCM 1704.*

# L'HISTOIRE DE L'ÉLECTRONIQUE (9)

En 1895, le physicien Wilhelm Conrad Röntgen découvrit, par hasard, une sorte de rayonnement dont il ne put déterminer le type, raison pour laquelle il le baptisa « rayons-X ». Il procéda à des expériences à base d'ionisation par impact et utilisait à cet effet un écran recouvert de matériau fluorescent. Au cours d'une expérience à haute tension (entre 30 et 50 kV), il constata la naissance d'un rayonnement de très courte durée capable de traverser sa main et qui paraissait subir une absorption plus importante au niveau des os qu'à celui de la chair. On voyait ainsi, brièvement il est vrai, les os apparaître nettement sur l'écran. Ce fut l'entrée en scène de ce qui est aujourd'hui le rayonnement de röntgen, découverte qui lui valut le premier prix Nobel de Physique jamais attribué.

Dès 1884, Edison procéda à des expériences utilisant une ampoule à incandescence dotée d'une plaquette métallique disposée en regard du filament. Il constata qu'il ne circulait de courant, du filament vers la plaquette, que lorsque cette dernière présentait un potentiel positif par rapport à celui du filament. 5 ans plus tard, Ambrose Fleming montra que le courant se composait de charges négatives, Joseph Thomson démontrant lui, en 1897, que les dites charges étaient en fait des électrons; il détermina également la masse de l'électron et sa charge. Thomson utilisa à cet effet un tube cathodique spécial. Au cours de la même année, Karl Ferdinand Braun décrivit un exemplaire spécial de ce type de tube : un cou de 30 cm de long d'évasant sous une forme conique de 15 cm avant de se terminer par un écran quasiment plat recouvert à l'intérieur d'un matériau phosphorescent. Les électrons sont attirés par la cathode et accélérés par la haute tension qui règne au niveau de l'anode située

Wilhelm Conrad

Röntgen (1845 - 1923)

10 cm plus loin environ. Dans le cou du tube les électrons percutent un diaphragme d'aluminium doté d'un orifice de 2 cm de diamètre. On obtenait ainsi un faisceau d'électrons concentré qui percutait l'écran phosphorescent et se manifestait, vu de l'extérieur, sous la forme d'un point lumineux. Par le biais d'une déviation électrostatique ou magnétique, Braun parvint à visualiser à l'écran le déroulement de phénomènes électriques. L'ancêtre de l'oscilloscope et la base du tube de télévision venaient ainsi de naître.

Dès 1875 le savant écossais James Maxwell pressentit les possibilités cachées des ondes électromagnétiques. Sur la base des théories développées dans son fameux ouvrage « A treatise on electricity and magnetism » on peut prouver que, dans certaines conditions, un conducteur électrique de transformera en source de rayonnement électromagnétique. Cette découverte intrigua nombre de savants et tant Heinrich Herz que David Hughes purent, aux alentours de 1889, confirmer expérimentalement la théorie de Maxwell. Le dernier nommé réussit à émettre réellement des signaux qu'il capta à une certaine distance et ce sans utiliser de liaison physique. Il ne saisit pas l'utilité pratique de cette découverte, ce qui ne fut pas le cas d'un certain monsieur Guglielmo Marconi. Ce dernier réussit, assez vite, à ponter des distances respectables et fut l'un des seuls à pressentir l'importance de la télégraphie sans fil. En 1898 il établit, en Angleterre, une liaison de 15 miles nautiques et en 1901 il ponta l'Océan Atlantique. Où en serions-nous sans Marconi !

(995089)

Guglielmo Marconi

(1874 - 1927)

# ADSL

## Accès haute vitesse à Internet

*jusqu'à 8 Mbits/s

par ligne téléphonique ordinaire*

Une nouvelle technique permet de se servir d'une ligne bifilaire normale pour transmettre des données à débit élevé : ADSL (*Asymmetric Digital Subscriber Line*) offre aux abonnés des télécoms la possibilité de multiplier le vitesse de leur accès Internet. Nous décrivons ici la technique ADSL et les offres déjà disponibles.

par Gregor Kleine

Presque chaque foyer dispose d'un raccordement téléphonique sous forme de paire torsadée de conducteurs de cuivre. En cherchant à accroître le débit dont dispose l'abonné sans recourir à de nouvelles liaisons ou aux fibres optiques, on a effectué des essais destinés à étudier l'aptitude de l'infrastructure existante à fournir des débits élevés. Les bases des méthodes xDSL actuelles, les Digital Subscriber Lines, datent d'il y a plus de 10 ans. Les méthodes DSL ont toutes recours à la paire de conducteurs de cuivre disponible pour multiplier le débit des données par un spectre de fréquence élargi. ADSL (*Asymmetric Digital Subscriber Line*) est actuellement au point et est offert par les télécoms et les exploitants de réseaux aux États-Unis et en Europe. Les procédé de modulation de ADSL CAP (*Carrierless Amplitude and Phase modulation*) et DMT (*Discrete MultiTone*) ont été discutés et testés. La norme ADSL T1.413 a été agréée

fin 1997 par ANSI (*American National Standards Institute*) et la modulation DMT, plus efficace que CAP, retenue à cet effet. Ce procédé de modulation est décrit ci-dessous.

### ADSL EN BREF

ADSL signifie *Asymmetric Digital Subscriber Line*. On entend par « Asymmetric » l'asymétrie des taux de transfert : Downstream indique le transfert du central au client. ADSL permet de transférer jusqu'à 8 Mbits/s au client dans ce mode. Le transfert du client au central par ADSL ne dépasse pas 1 Mbits/s. On parle de direction Upstream (montant), car les données du client doivent quasiment lutter contre le courant pour parvenir au central. En pratique, on n'atteint toutefois pas tout à fait les taux maxima car les grandeurs parasites de la paire de cuivre peuvent réduire sensiblement le débit. Le processus de transmission est adaptif, c'est-à-dire qu'il adapte le débit aux condi-

tions du raccordement. ADSL s'adapte même dynamiquement au cours d'une communication lorsque les grandeurs parasites (par exemple la diaphonie causée par une autre ligne téléphonique du faisceau) varient.

Les débits downstream (descendant) et upstream les plus élevés possibles dépendent donc fortement des caractéristiques du raccordement utilisé : la longueur de la liaison avec le central joue un rôle décisif. La distance entre le centre et l'abonné est en moyenne d'environ 2 km en Allemagne. Seul un nombre restreint de lignes dépassent 4 km. ADSL permet normalement de transférer de 6 Mbit/s à 8 Mbit/s par des lignes ne dépassant pas 3 km sans perturbations excessives. La section des conducteurs d'un raccordement d'abonné constitue un autre facteur de qualité. Le torsadage des conducteurs signifie en principe que l'impédance de la ligne est constante, mais cette situation idéale peut être fortement compromise par les épissures, le passage à d'autres types de conducteurs, les boîtiers de connexion et les terminaux raccordés. Le débit maximum est alors plus ou moins fortement limité par le signal réfléchi aux points de réflexion. La qualité du câblage chez l'abonné n'est enfin pas le moindre facteur déterminant la vitesse du débit downstream. L'utilisation des autres conducteurs du faisceau joue aussi un rôle. S'ils assurent aussi des transmissions ADSL, il faut compter avec la diaphonie entre paires voisines. Une commutation des conducteurs pour améliorer le découplage des deux itinéraires ADSL améliore parfois la situation, à condition que le trafic ADSL ne soit pas trop élevé.

Les champs d'application de la technique ADSL sont constitués par tous les services multimédias qui sont indubitablement les principaux consommateurs actuels d'accès rapide à Internet. Les premiers essais d'ADSL ont toutefois aussi porté sur l'acceptation dans les domaines du téléchargement, de l'enseignement à distance, de la vidéo à la demande, de la musique à la demande et ainsi de suite.

## LE SPECTRE ADSL

### Un signal DMT ADSL

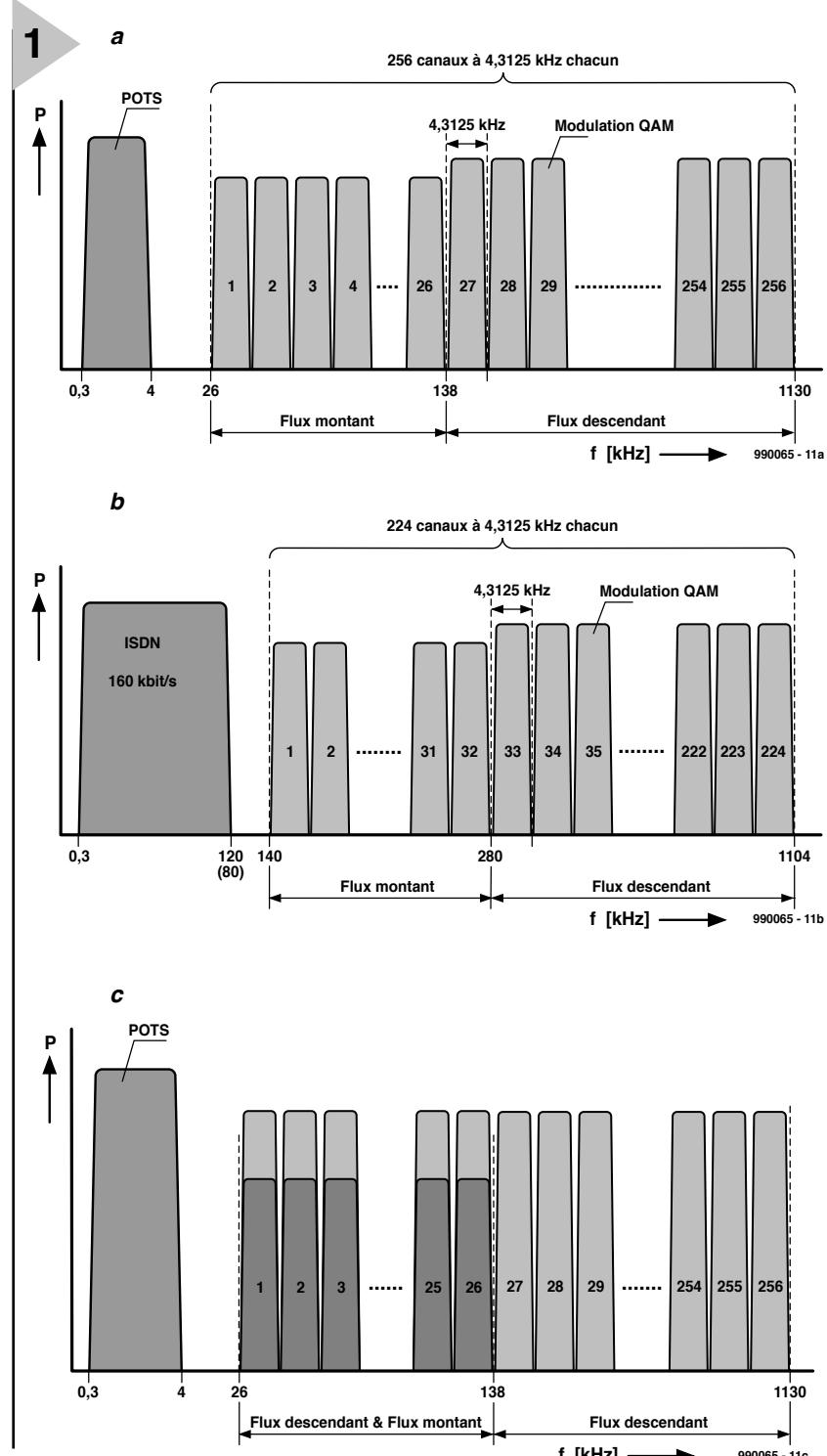

est composé en majeure partie d'un grand nombre de porteuses modulées indépendamment qui sont transmises par les deux fils de cuivre au-delà de la bande normale de la parole. La **figure 1** représente le spectre de fréquence du signal : la norme ADSL initiale prévoit de laisser libre la gamme de fréquence entre 0 et 26 kHz pour la téléphonie analogique actuelle (POTS = Plain Old Telephone Service). Outre la bande

**Figure 1. Spectre ADSL dans le cas de**

**a) la télémétrie analogique (fonctionnement FDM)**

**b) RNIS (fonctionnement FDM)**

**c) la télémétrie analogique (fonctionnement avec compensation d'écho).**

vocale (de 300 Hz à 4,3 kHz), cette gamme contient des signaux tels que les impulsions de taxation (allemandes) de 16 kHz. Entre 26 kHz et 1,130 MHz se trouvent 256 canaux, occupant chacun 4,3125 kHz de largeur de bande. Les fréquences centrales des canaux sont aussi distantes de 4,3125 kHz. Chaque porteuse upstream et downstream est modulée QAM (amplitude en quadrature) et contient entre 2 bits/s

par Hz et un maximum de 15 bits/s par Hz. Le débit des informations est adapté, c'est-à-dire que chaque porteuse se voit attribuer son propre paramétrage QAM (... , 64QAM, 32QAM, 16QAM, 8QAM, QPSK) lors de la phase d'initialisation en fonction du rapport signal/bruit. Plus la distance signal/bruit est élevée et plus l'échelon de paramétrage QAM est élevé, et donc plus les bits/s et les Hz le sont. Une porteuse individuelle du signal DMT peut donc juste transmettre 64,7 kbit/s, ce qui représente théoriquement une capacité maximale de plus de 16 Mbit/s avec 256 porteuses.

2

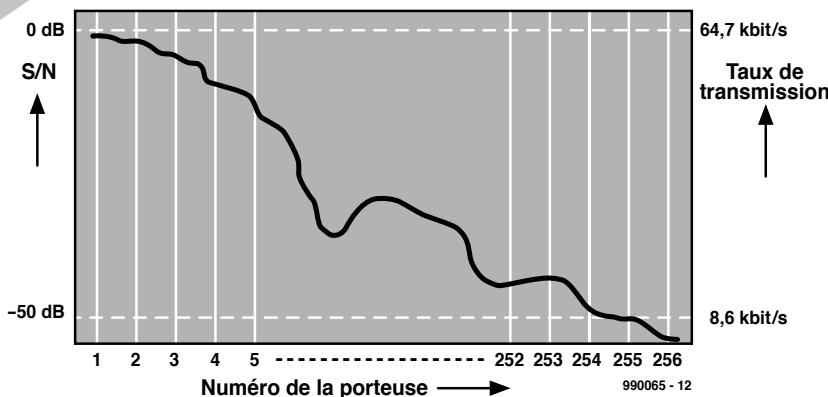

**Figure 2. Distribution des bits selon le rapport signal/bruit.**

On voit que même si les conditions de liaison sont optimales, seule la moitié de cette capacité est utilisable.

Comme on l'a déjà fait remarquer, de mauvaises conditions de liaison ou une longueur relativement élevée de celle-ci ont pour effet de diminuer l'occupation des bits d'une porteuse, donc le degré de modulation QAM lors de l'établissement de la liaison pour assurer une transmission fiable avec cette porteuse. Il peut même arriver que des plages entières de porteuses soient éliminées du signal DMT parce qu'une atténuation trop élevée, des sources de perturbations locales, etc. rendent les fréquences correspondantes inutilisables. Il va sans dire qu'on peut alors faire une croix sur les 8 Mbit/s.

Selon la norme, il existe deux façons d'attribuer chaque porteuse downstream et upstream : on peut faire appel au mode de fonctionnement FDM (*Frequency Division Multiplexing*, **figure 1a** et **figure 1b**) qui est relativement peu complexe pour répartir les gammes de fréquence entre downstream et upstream. Les 26 premières porteuses constituent le canal upstream, tandis que les porteuses 27 à 256 contiennent les données downstream. On peut

aussi, selon la norme ADSL, travailler en mode de compensation d'écho. Dans ce

cas, les directions downstream et upstream se partagent une gamme de fréquence commune (porteuses de 1 à 26). Le terminateur permet de séparer les données downstream et upstream selon leur direction (**figure 1c**). Cela conduit bien entendu à une capacité accrue du flux de données en direction downstream, car les 112 kHz initiaux de la bande ADSL contiennent les porteuses qui peuvent être correctement transmises. Les fréquences plus élevées sont plus fortement amorties. Pour que ce processus fonctionne correctement, il est indispensable d'utiliser un correcteur d'écho qui élimine le restant éventuel de l'autre flux de données. La norme ADSL décrit par ailleurs ce second procédé d'attribution des fréquences sous le nom de *Category 2 ADSL*.

Les différences de niveau atteignant 50 dB entre les porteuses inférieures et supérieures sont provoquées par les distorsions dues à l'atténuation et doivent être détectées par les égaliseurs de canaux extrêmement raffinés du modem ADSL. Les porteuses trop affaiblies ne peuvent transmettre les

données. Grâce au codage dynamique des conducteurs (qui dépend du rapport signal/bruit mesuré) et à l'égalisateur de canaux, on parvient toutefois à tirer parti de conditions aussi défavorables pour effectuer la transmission de données. La **figure 2** reproduit schématiquement le comportement du rapport S/N et du débit binaire attribué en fonction du numéro de porteuse (1 à 256).

## ADSL ET RNIS

La figure 1b indique les conditions pour les abonnés à raccordement téléphonique numérique RNIS. Le signal RNIS de  $2 \times 64$  kbit/s (128 kbit/s) s'étend normalement jusqu'à 80 kHz. En Allemagne, sa bande de fréquence s'étend même jusqu'à 120 kHz. Pour pouvoir aussi offrir ADSL comme extension à vitesse élevée avec des raccordements RNIS, il a fallu trouver une méthode de combiner les signaux ADSL à RNIS. Il aurait été possible d'utiliser alternativement RNIS et ADSL selon les besoins. Mais cela aurait eu pour conséquence de lier RNIS et ADSL et d'empêcher leur utilisation simultanée. C'est pourquoi on a décidé de s'écartier de la norme en ne faisant commencer le signal DMT qu'à 140 kHz. Si la distance entre porteuses et la largeur de bande de la modulation restent inchangées (4,3125 kHz chacune), il ne reste que 224 porteuses. Cette solution a été justifiée et recommandée à posteriori dans l'annexe B de la norme ADSL.

Le problème que cette méthode pose avec RNIS est que les porteuses les plus basses sont réservées, selon la norme ADSL, au test de la liaison lors de la connexion par des séquences d'apprentissage et à la détermination du débit binaire de chaque porteuse DMT. Comme elles sont inaccessibles dans le cas de la solution RNIS, force est de recourir à d'autres porteuses du domaine upstream pour l'établissement de la connexion, en contradiction avec la norme ADSL. L'annexe B

3

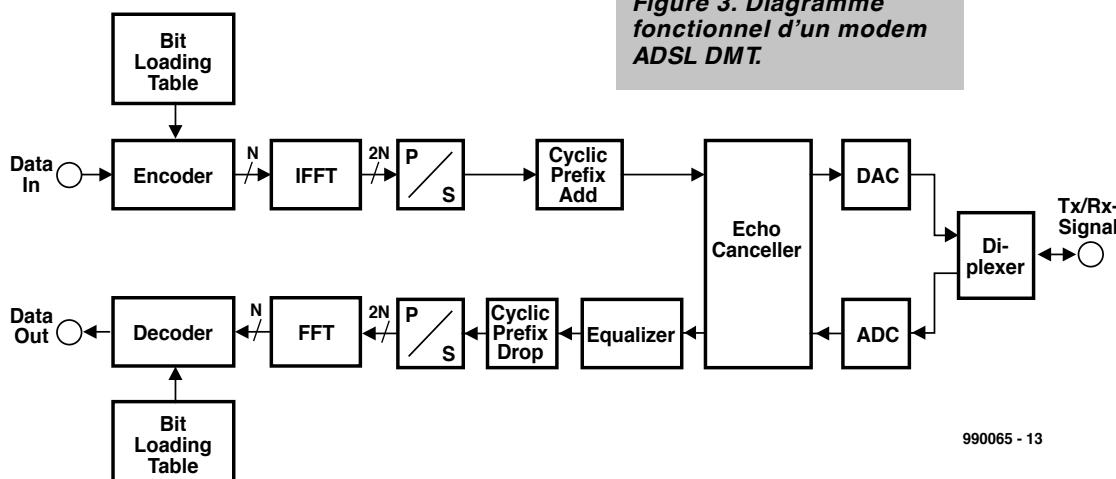

**Figure 3. Diagramme fonctionnel d'un modem ADSL DMT.**

990065 - 13

contient la description de ce procédé. La raison pour laquelle on fait appel aux porteuses les plus basses lors de l'établissement de la connexion est qu'elles sont celles qui, à ce moment-là, peuvent être transmises le plus loin dans la ligne de l'abonné, de sorte que l'établissement initial de la connexion avec le modem ADSL d'un abonné, même éloigné (3 à 4 km), reste toujours possible.

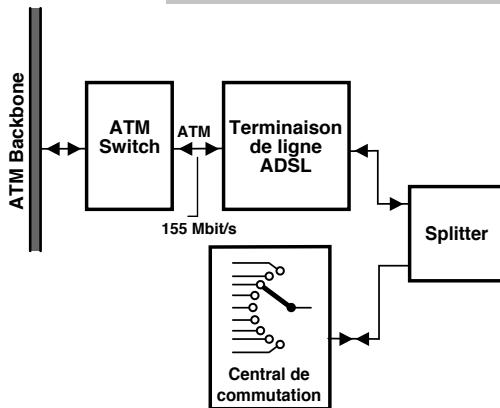

## STRUCTURE DES MODEMS ADSL

La structure des modems utilisés avec ADSL est représentée de manière schématique et simplifiée dans la **figure 3**. Le circuit est en principe identique côté central. La seule différence réside dans la distribution d'ADSL à plusieurs abonnés (par exemple 4). On parle alors aussi de DSLM (*Digital Subscriber Line Multiplexer*).

Les données envoyées (données upstream côté abonné, données downstream côté central) sont transmises à un codeur qui attribue les N porteuses du signal DMT. Cela est effectué sur la base du tableau de chargement des bits (*Bit Loading*) créé lors de l'établissement de la connexion qui indique le nombre de bits/s que chaque porteuse est en mesure de transmettre. Le codeur effectue aussi une correction Reed-Solomon FEC (*Forward Error Correction*). Les bits sont ensuite traités en parallèle par un C.I. qui effectue une IFFT (transformée de Fourier rapide inverse). On obtient ainsi à partir du spectre numérique de fréquence sur N bits des porteuses individuelles le signal temporel associé sous forme de nombre complexe de 2N bits (partie réelle + partie imaginaire). Un en-tête de synchronisation est ajouté cycliquement après la conversion parallèle/série. La distorsion des signaux émis et reçus provoquée intentionnellement par le suppresseur d'écho compense les échos de la liaison. Il se règle automatiquement lors de l'établissement de la connexion par une séquence d'apprentissage. Le signal émis (Tx) peut être finalement être converti D/A et envoyé à la ligne au moyen d'un diplexeur séparant les voies d'émission et de réception.

Le signal reçu (Rx) passe d'un diplexeur à un convertisseur A/D qui envoie lui aussi le signal d'entrée numérisé à un suppresseur d'écho. Comme pour l'émission, le suppresseur d'écho « répare » les dommages causés par l'écho de la liaison au flux de données reçu. Un égaliseur, toujours réglé correctement par des séquences d'apprentissage lors de l'établissement de la connexion, puis lors de l'utilisation de celle-ci, élimine la distorsion de la courbe de réponse. L'en-tête du flux de données est ensuite extrait. Une fois la conversion

**Tableau 1. Adresses sur Internet des fabricants de circuits intégrés ADSL**

| Fabricant           | Page d'accueil Internet                                      |

|---------------------|--------------------------------------------------------------|

| Motorola            | <a href="http://www.mot-sps.com">www.mot-sps.com</a>         |

| ST Microelectronics | <a href="http://www.st.com">www.st.com</a>                   |

| Alcatel             | <a href="http://www.usa.alcatel.com">www.usa.alcatel.com</a> |

| Broadcom            | <a href="http://www.broadcom.com">www.broadcom.com</a>       |

| GlobeSpan           | <a href="http://www.globespan.net">www.globespan.net</a>     |

| Texas Instruments   | <a href="http://www.ti.com/sc">www.ti.com/sc</a>             |

série/parallèle effectuée, un segment exactement défini du signal temporel numérisé est envoyé au composant FFT (*Fast Fourier Transform*) sous forme de mot de 2N bits. La transformée de Fourier rapide permet de revenir des 2N bits du domaine temporel au domaine de fréquence, ce qui fournit les états de phase de la porteuse modulée QAM sous la forme de N bits en parallèle. Le décodeur doit enfin replacer les bits de chaque porteuse DMT dans le bon ordre sur la base d'un tableau de chargement des bits chargé à cet effet. Il inverse toutefois en premier lieu le codage Reed-Solomon, dont la puissance permet de corriger de nombreux bits erronés.

Un grand nombre de fabricants de semi-conducteurs sont actuellement en mesure d'offrir des jeux de puces et autres composants spécialement destinés aux modems ADSL. Citons Motorola (jeu de puces Copper Gold), STMicroelectronics, Alcatel (jeu de puces DynaMite), Broadcom, GlobeSpan et Texas Instruments. Vous trouverez les adresses WWW de ces entreprises dans le **tableau 1**.

Les modems ADSL constituent aussi un défi pour les réalisateurs dans le domaine analogique. Le signal DMT exige une linéarité très poussée des amplificateurs et des circuits attaquant les lignes. Le facteur de crête (rapport entre la puissance de pointe et la puissance effective) est très élevé, ce qui

veut dire que les circuits d'attaque doivent comporter de fortes réserves. C'est la raison pour laquelle des fabricants comme Burr Brown et Analog Devices offrent des C.I. spécialement conçus à cet effet. L'équipement des centraux pose, lui aussi, quelques problèmes, car il faut prévoir jusqu'à 12 W par raccordement ADSL dans le bâti des liaisons d'abonnés. La dissipation de chaleur devient le problème majeur lorsque le matériel est disposé de façon compacte.

## ÉQUIPEMENT DES LIAISONS ADSL

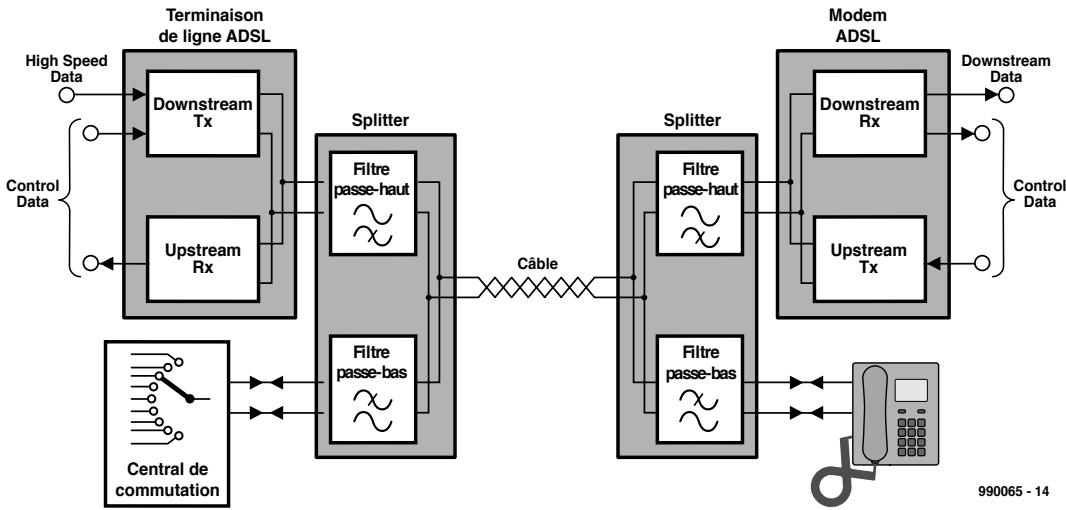

Comment un raccordement téléphonique ADSL se présente-t-il côté abonné et côté central ? La **figure 4** le révèle en détail. Chacun des deux diviseurs ADSL connectés au départ même du raccordement côté central et abonné contient d'excellents filtres passe-haut, c'est à dire à flancs raides, pour le spectre ADSL. Des filtres passe-bas se chargent de filtrer le signal analogique usuel du téléphone ou le signal RNIS sur la liaison de raccordement et à partir de celle-ci. Le diviseur de l'abonné qui veut se servir de ADSL doit bien entendu être raccordé à un modem de ce type. Le modem comporte un récepteur (RX) du signal downstream à débit élevé et un émetteur (TX) destiné au signal upstream envoyé par l'abonné. Les données upstream et downstream contiennent les

### Abréviations

|      |                                                                                      |

|------|--------------------------------------------------------------------------------------|

| ADC  | <i>Analog to Digital Converter, convertisseur A/N</i>                                |

| ADSL | <i>Asymmetric Digital Subscriber Line</i>                                            |

| ATM  | <i>Asynchronous Transfer Mode, mode de transfert asynchrone</i>                      |

| DAC  | <i>Digital to Analog Converter, convertisseur N/A</i>                                |

| DSL  | <i>Digital Subsiber Line</i>                                                         |

| DSLM | <i>Digital Subsciber Line Multiplexer</i>                                            |

| FFT  | <i>Fast Fourier Transformation, transformation de Fourier rapide</i>                 |

| IFFT | <i>Inverse Fast Fourier Transformation, transformation de Fourier rapide inverse</i> |

| ISDN | <i>Integrated Services Digital Network</i>                                           |

| NTBa | <i>Network Termination Base connection</i>                                           |

| PC   | <i>Personal Computer</i>                                                             |

| POTS | <i>Plain Old Telephone Service, Services de téléphone analogique</i>                 |

| QAM  | <i>Quadrature Amplitude Modulation, Modulation en amplitude en quadrature</i>        |

| RX   | <i>Receiver, récepteur</i>                                                           |

| TX   | <i>Transmitter, émetteur</i>                                                         |

4

**Figure 4. Schéma de principe de l'équipement de ligne ADSL.**

données utiles plus des données de gestion et de commande.

Il faut que le central puisse commuter tous les abonnés qui le désirent sur des terminaisons de ligne ADSL. Ces terminaisons constituent le complément du modem ADSL : un émetteur downstream (TX) transmet le flux de données à débit élevé au raccordement en passant par le diviseur. Le débit des données du récepteur upstream (RX) n'est que moyen. Un multiplexeur DSLM (Digital Subscriber Line Multiplexer) permet de répartir les canaux ADSL entre plusieurs abonnés

## STRUCTURE DU SYSTÈME ADSL

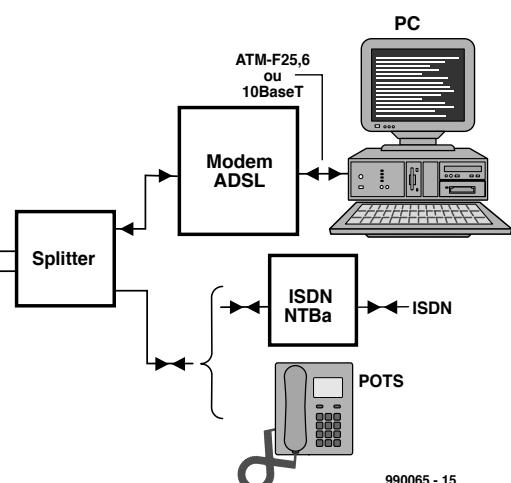

Quelle est la suite des opérations, une fois sorti de l'équipement de liaison ADSL et du modem ADSL ? La figure 5 donne la réponse. On rencontre encore les diviseurs du central et des abonnés. La terminaison de ligne ADSL y est connectée dans le central. Elle est raccordée à 155 Mbits/s à la dorsale ATM par un commutateur ATM.

Le côté abonné com-

porte un modem ADSL équipé d'une interface ATM F25,6 (25,6 Mbits/s) ou d'une

interface LAN (plus lente) 10BaseT. Le PC qui suit doit disposer d'une carte ATM ou réseau idoine pour commander parfaitement l'interface du modem ADSL. La figure 5 indique que, dans le cas de RNIS également, il faut intercaler la terminaison NTBa (Network Termination, terminaison du réseau de l'accès de base) à la suite du diviseur.

## ÉTABLISSEMENT DE LA CONNEXION

Les nombreuses possibilités de réglage d'un système de transmission ADSL requièrent, lors de l'établissement de la connexion, l'échange d'un protocole complexe qui permet au central et au modem ADSL de se communiquer leur configuration respective. Les deux modems saisissent les courbes de réponse dans les deux directions de transmission en envoyant des fréquences pures (porteuses) dont le niveau sera enregistré par l'autre modem. Le débit binaire des canaux downstream et upstream ainsi que le

procédé à utiliser pour séparer les directions (FDM ou compensation d'écho) est ensuite déterminé au moyen d'une séquence d'apprentissage. C'est à ce point que se décide le débit binaire maximum réalisable des lignes de raccordement individuelles. ADSL peut aussi venir à bout de perturbations variant dans le temps. L'échange de bits (Bit Swapping) permettra de modifier en direct l'attribution des bits aux porteuses.

Cette phase de démarrage passablement élaborée de ADSL prend plus de 20 secondes et même parfois plus d'une minute. Mais c'est le prix à payer pour optimiser le débit de chaque porteuse.

Lorsqu'une connexion ADSL est déjà établie, il peut arriver qu'un changement brusque des paramètres de la liaison dérègle à tel point les paramètres soigneusement mis au point de l'égaliseur que la capacité de transfert s'affondre brusquement. Il faut naturellement éviter que la correction de l'égaliseur permettant de rétablir complètement la liaison ne dure de nouveau 20 à 60 secondes. Il est donc possible d'avoir recours à une procédure de réglage abrégée qui détermine

**Figure 5. Structure du système lors de l'adoption de ADSL.**

5

rapidement les nouveaux paramètres de l'égaliseur en se basant sur les paramètres de la liaison déterminés lors de l'établissement de la connexion. La liaison ADSL est en général rétablie au bout de 1 à 2 secondes. Cela exige toutefois que le modem ADSL surveille continuellement la qualité de transmission de chaque porteuse.

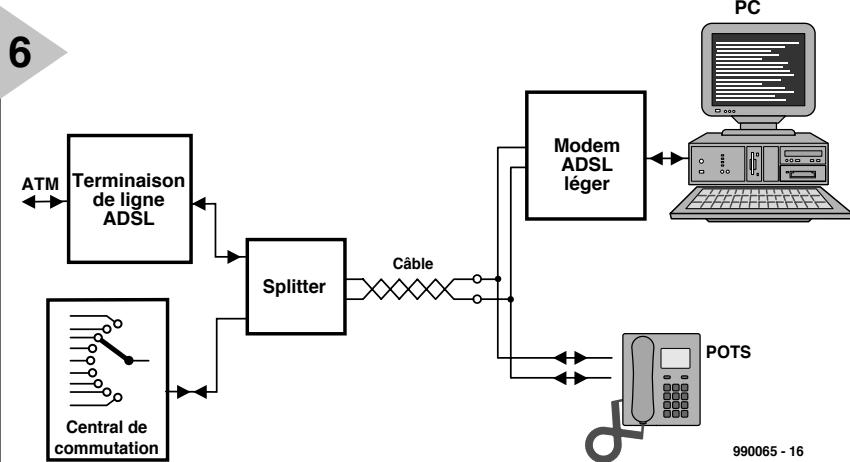

## ADSL ALLÉGÉ

Une fois la norme ADSL définie, un groupe de fabricants (parmi lesquels Microsoft, Intel et Compaq) ont fondé le groupe de travail UAWG (*Universal ADSL Working Group*). Leur but était de se débarrasser du diviseur côté abonné, considéré jusque là comme indispensable. L'équipement d'un canal ADSL côté central se limiterait ainsi à la terminaison de ligne (SLIC = *Subscriber Line Interface*) et du côté abonné à un modem ADSL et une carte réseau ATM/Ethernet. Le diviseur côté abonné, qui n'est pas précisément bon marché, serait éliminé (figure 6). Ce procédé dénommé aussi 'G.Lite' ou 'Universal ADSL' a été normalisé par l'UIT en tant que *ITU-Standard G992.2 - Splitterless ADSL*.

Non content de « soustraire » le diviseur de G.Lite, on a encore divisé par 2 le nombre de portes (128 au lieu de 256). Le nombre de bits par seconde et de hertz passe donc de 15 à 8 et les configurations QAM sont simplifiées d'autant. Le taux downstream est réduit à environ 1,5 Mbit/s, tandis qu'il est encore possible de faire parvenir 500 kbit/s upstream. Il est en outre possible de réduire à tel point le niveau de sortie que la puissance absorbée et les impératifs de linéarité des étages d'attaque analogiques s'en trouvent fortement réduits. Cela garantit aussi un fonctionnement sans diviseur dépourvu interférences du téléphone analogique (POTS). Enfin, ADSL Lite s'efforce d'atteindre le niveau d'exploitation Category 2 dans lequel upstream et downstream se partagent la gamme inférieure de fréquence ADSL grâce à la compensation d'écho. Cela assure de bonnes conditions de transmission pour toutes les portes.

La simplification que cette forme d'ADSL représente pour le client en constitue la motivation. Outre les coûts du diviseur, on peut aussi tirer un trait sur l'alimentation par la prise de l'abonné (embase femelle). Les coûts de montage à domicile du diviseur ADSL et de sa mise en service disparaissent. Les spécialistes font toutefois remarquer que ADSL Lite ne fonctionnera du premier coup que dans la moitié des foyers. Il faudra tout d'abord corriger le câblage domestique de l'autre moitié.

Alors qu'une forte tendance en direction de ADSL Lite se dessine aux États-Unis, l'Europe serait plutôt sceptique.

**Figure 6. ADSL Lite.**

La majorité des systèmes ADSL installés ici le seront avec un diviseur côté abonné.

## ADSL – POUR QUI ?

Si l'on suppose qu'une longueur de connexion d'environ 3 km marque la limite d'utilisation de ADSL, il est possible de fournir à 85 % des abonnés ces services de données rapides.

Ne pourront être raccordés par ADSL tous les abonnés qui ne disposent pas de leur propre liaison dans le central mais dont les lignes de raccordement sont déjà réunies auparavant par multiplexeurs (systèmes PCM2, PCM4 et AsIMx). Il s'agit d'environ 10 % des raccordements téléphoniques en Allemagne.

## EN GUISE DE CONCLUSION

ADSL est une nouvelle technologie qui permet de mieux tirer parti des liaisons téléphoniques actuelles. Même si les raccordements ADSL privés ne fournit tout d'abord que 1,5 Mbit/s downstream, cela signifie quand même un accroissement de la vitesse de 27 par rapport aux modems 56K usuels. Il sera possible de faire son entrée dans la technique ADSL

par ce que l'on nomme des modems hybrides capables de traiter aussi bien la norme analogique V.90 qu'ADSL. Les adaptations à tout changement des normes restera toujours possible par téléchargement de modules de micrologiciel.

Et quel sera le successeur d'ADSL ? Réponse : VDSL, Very high bit-rate Digital Subscriber Line. Les laboratoires de recherche indus-

trielle travaillent à l'extension du

domaine de fréquence vers le haut, donc à l'accroissement du nombre de portes. Avec 2 000 portes, il est possible d'atteindre un débit de 52 Mbit/s downstream et un accroissement de 3,2 Mbit/s de capacité upstream. Cela devrait suffire pour transférer le flot de données vidéo MPEG-2. Un petit inconvénient : VDSL a besoin de lignes de raccordement encore plus courtes que ADSL, maximum 1,5 km. La solution serait naturellement de passer aux fibres optiques pour couvrir la distance du central aux armoires de distribution qui bordent les voies publiques. Mais il coulera jusqu'à là encore beaucoup d'eau sous les ponts.

(990065)

### Références :

- ANSI-Standard T1.413

- ITU-Standard G992.1 (Annex B: RNIS + ADSL)

- ITU-Standard G992.2 - Splitterless ADSL

### Infos sur le WWW :

- [www.dtag.de](http://www.dtag.de)

- [www.adsl.com](http://www.adsl.com)

- [www.uawg.org](http://www.uawg.org)

# chargeur d'accus HP (2)

## *construction, étalonnage et mode d'emploi*

Comme vous avez sans doute pu le constater à la lecture du premier article publié le mois dernier et consacré à la description et au fonctionnement de notre chargeur Hautes Performances d'où notre HP, la réalisation d'un tel projet au courant pouvant atteindre jusqu'à 8 A, est plus intéressante que celle du chargeur d'accu lambda. Ce second article prend une importance capitale pour la réussite de ce projet. On y trouvera, outre la description de la réalisation et de l'étalonnage au cours duquel le micro-contrôleur constitue un auxiliaire précieux, également des informations importantes sur son mode d'emploi et sur les soins à porter aux accus.

Permettez-nous une remarque préliminaire : le présent chargeur d'accus HP n'est pas un projet à tenter par un débutant en électronique. Non seulement on a affaire à une électronique relativement complexe requérant l'un ou l'autre réglage mais également à un courant d'une certaine intensité (8 A au maximum comme nous le disions), ce qui implique un risque non imaginai de dommages importants en cas de court-circuit. Si vous avez déjà réalisé

avec succès un amplificateur audio de bonne puissance ou une alimentation de laboratoire, ce projet de forte puissance ne devrait pas poser de problème, à condition bien entendu de travailler avec soin.

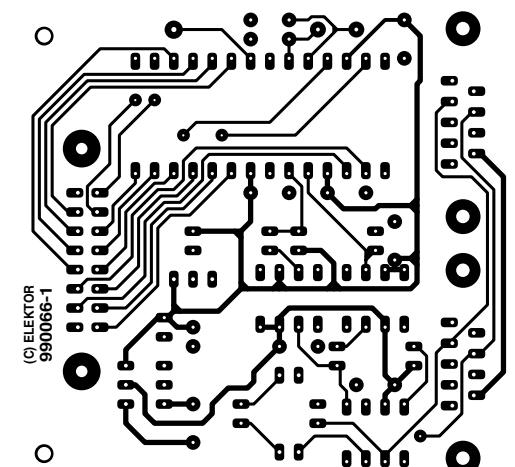

### LA RÉALISATION

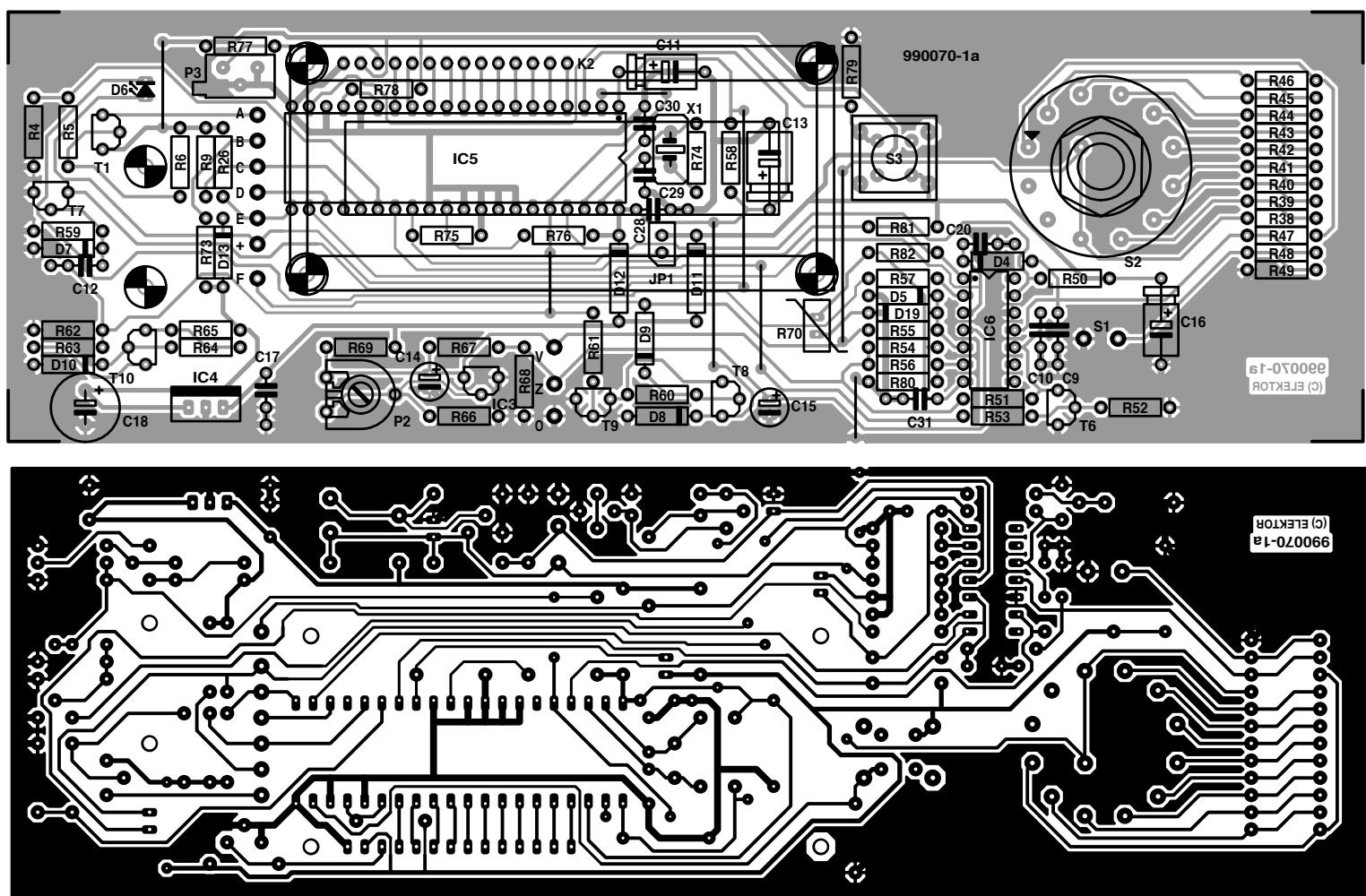

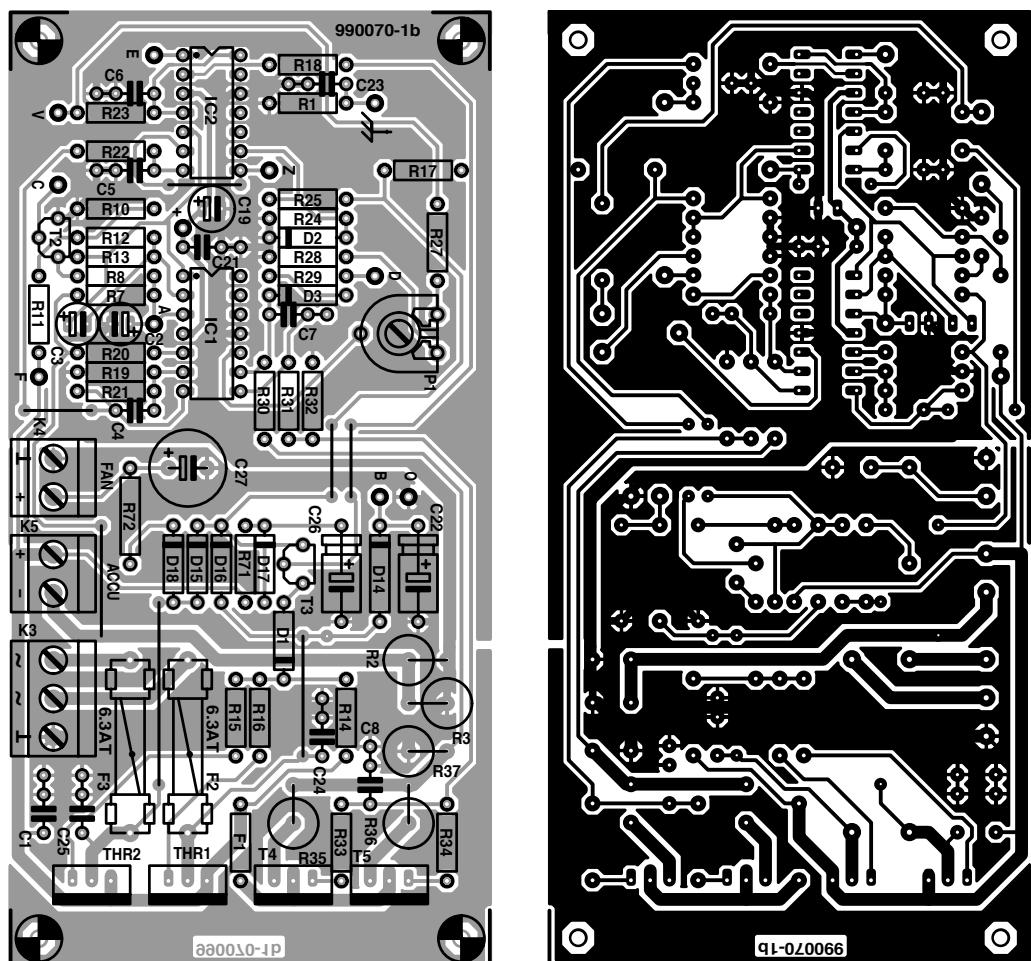

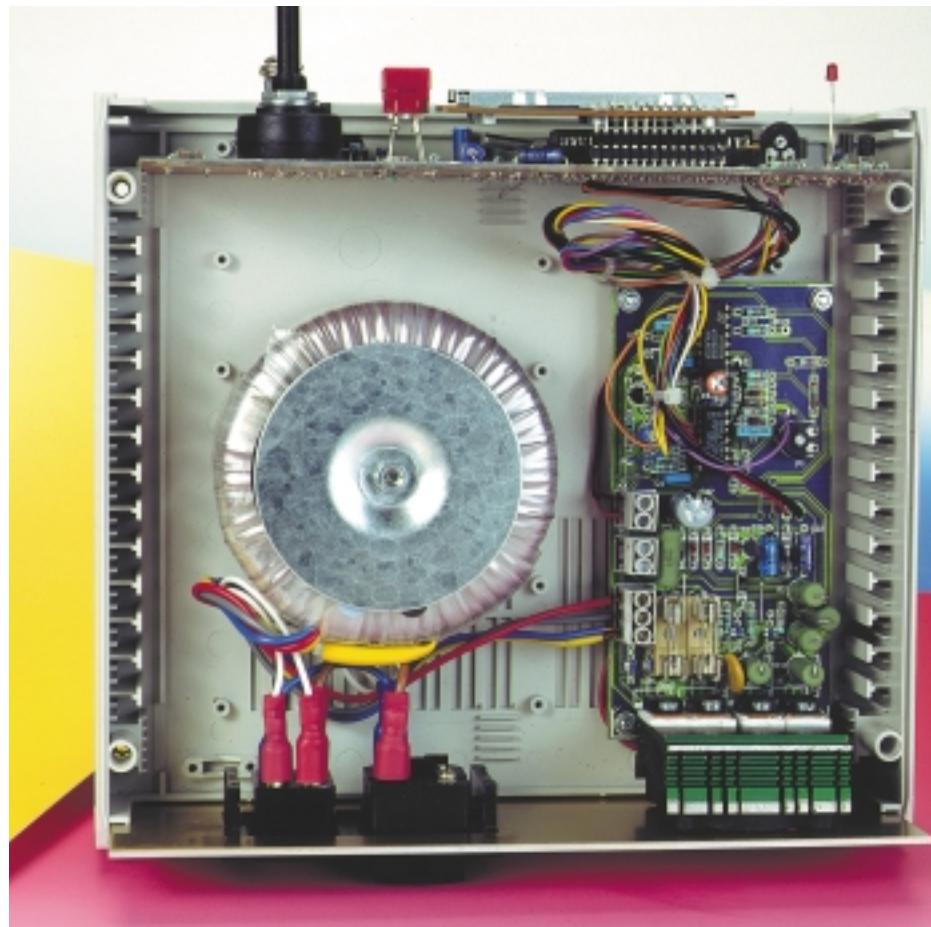

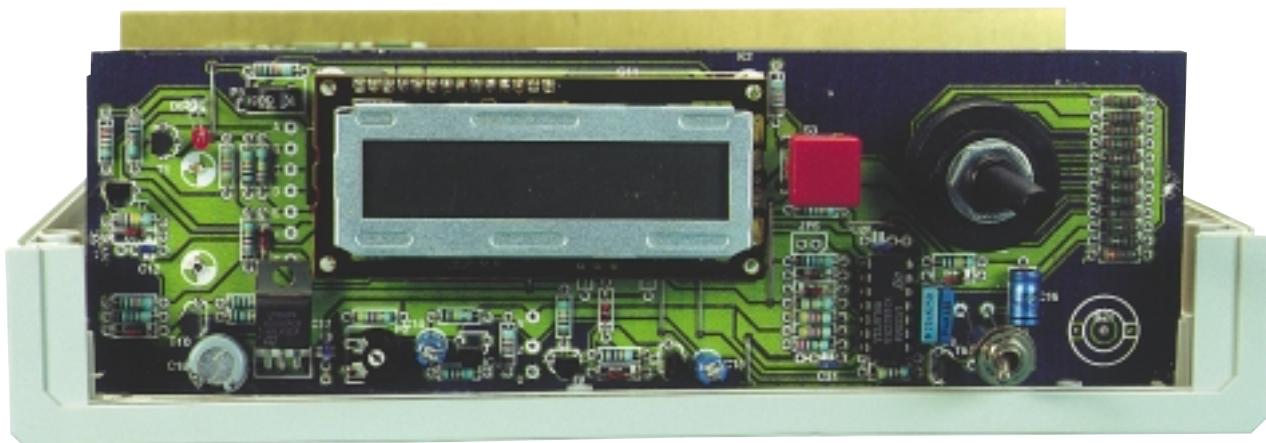

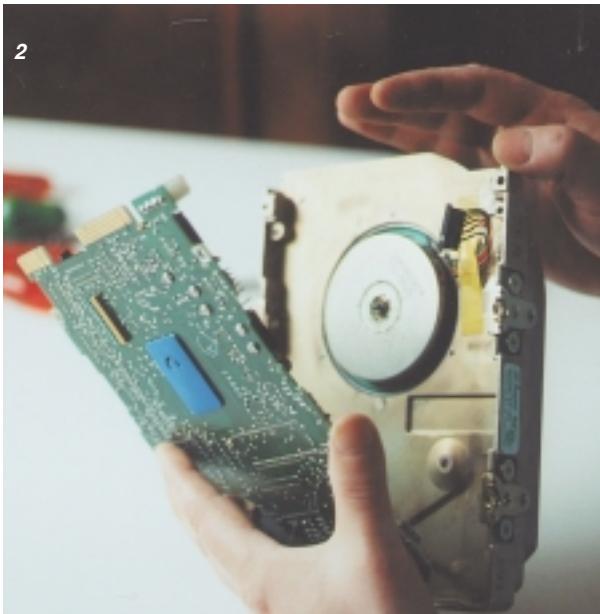

Le montage se fait sur une paire de plaques simple face (**figures 1 et 2**) à séparer l'une de l'autre avant de débuter l'opération d'implantation des compo-

projet : Norbert Bechtloff

et Günther Brenner

(Conrad-Technology-Center CTC)

sants. L'approche simple face se paie par un certain nombre de ponts de câblage. On débutera donc par la mise en place des ponts de câblage pour vérifier ensuite que l'on a bien, comme l'illustre la sérigraphie, implanté 7 ponts (au bon endroit !) sur la petite platine et 8 sur la grande. On placera de préférence l'embase du cavalier de court-circuit JP1 côté « pistes » de la platine de face avant de manière à pouvoir planter le cavalier même lorsque la platine aura été dotée, côté « composants », du module LCD. IC4 de la platine principale sera à monter couché pour éviter que son boîtier n'entre en contact avec la face avant. La touche S3, l'inverseur S1 et la LED D6 seront montés, au début, de façon provisoire sur la platine principale. Une fois les étapes de test et d'équilibrage terminées avec succès, ces composants prendront leur place définitive dans la face avant et seront reliés à la platine à l'aide de fil de câblage souple. Le processeur ne prend pas encore place dans son support, l'affichage LCD n'étant pas connecté non plus sachant que ces 2 composants ne sont pas nécessaires pour effectuer les 2 premiers réglages (tension du ventila-

teur et surveillance de la température). La surveillance de la température est optionnelle et ne requiert pas d'être impérativement mise en place. On pourra, si l'on opte de ne surveiller ni la température du radiateur ni celle de l'accu, omettre d'implanter non seulement la NTC mais aussi les résistances R54, R56, R80 et R92 (R81 devra **toujours** être montée). La NTC sera une résistance à coefficient de température négatif ayant une résistance à froid comprise entre 500 et 1 000  $\Omega$ . Le réglage de la température de consigne du circuit se fait par mesure de R80, comme nous le verrons dans le paragraphe « L'équilibrage ».

L'utilisation d'un radiateur pour CPU à ventilateur intégré en place et lieu de radiateur normal appelle quelques commentaires. On peut, en principe, utiliser n'importe quel refroidisseur de CPU courant. Il est important cependant de veiller à ce que les transistors soient isolés, montage que l'on fera à l'aide de plaquettes de céramique enduites des 2 côtés de pâte thermooconductrice. Les orifices des vis de fixation seront percés à la mèche de 2,5 ou de 2,7 mm. On vérifiera, à l'ohmmètre, que les transistors sont parfaitement

isolés l'un par rapport à l'autre avant de monter le refroidisseur; comme le transformateur peut fournir des courants importants, tout court-circuit aurait des conséquences pour le moins désagréables.

On veillera, lors de la mise en boîtier à ce que le flux d'air puisse s'établir sans rencontrer d'obstacle. On perce, dans la face arrière, la plaque de métal qui vient se glisser dans les rails arrières du boîtier, un orifice de diamètre égal à celui du ventilateur. On pourra, pour une ventilation optimale, doter le boîtier de fentes de ventilation additionnelles.

La mesure de la résistance du ventilateur, R72, fera elle aussi l'objet d'une description dans le paragraphe « L'équilibrage ».

Les photos montrent les plaques dotées de leurs composants respectifs et leur montage dans le coffret. Il est important de veiller à une parfaite isolation lors de la connexion du transformateur à l'embase secteur, toutes les parties véhiculant la tension du secteur doivent être parfaitement isolées pour éviter tout risque en cas de contact accidentel.

Le secondaire du transformateur comporte la plupart du temps 4 fils, le gris et le rouge représentant les lignes extérieures, les fils jaune et bleu une fois

**Figure 1. La platine principale sur laquelle se trouvent le microcontrôleur, les organes de commande et l'affichage LCD vient de placer derrière la face avant.**

## Liste des composants

Résistances :

R1,R25,R67,R75,R76,R82 = 100 kΩ

R2,R3,R37 = 0 Ω 1/5 W

R4,R21,R52,R79,R81 = 22 kΩ

R5,R9,R14,R18,R61,R66,R71 = 10 kΩ

R6,R78 = 47 kΩ

R7 = 33kΩ 2%

R8 = 15kΩ 2%

R10 = 750 Ω 1%

R11 = 1 MΩ 1%

R12 = 9kΩ 0.2% 1%

R13 = 215 kΩ 1%

R15,R16,R33,R34 = 100 Ω

R17,R53,R56,R77 = 4kΩ 2%

R19,R20 = 3kΩ 3%

R22,R64 = 1 kΩ

R23 = 487 kΩ 1%

R24 = 33 kΩ

R26,R50,R59 = 220 kΩ

R27 = 3kΩ 0.2% 1%

R28 = 237 Ω 1%

R29,R62 = 15 kΩ

R30,R68 = 2kΩ 2%

R31 = 390 Ω

R32 = 27 kΩ

R35,R36 = 0.27/5 W

R38 à R46 = 20 kΩ 1%

R47,R48 = 10 kΩ 1%

R49 = 3kΩ 0.2% 1%

R51 = 178 kΩ 1%

R54 = 5kΩ 0.2% 1%

R55 = 470 kΩ

R57 = 5kΩ 2%

R58 = 150 kΩ

R60 = 1 MΩ

R63 = 1kΩ 2%

R65 = 1kΩ 2%

R69 = 470 Ω

R70 = NTC 500 Ω \*

R72 = 27 Ω/2 W \*

R73 = 220 Ω

R74 = 10 MΩ

R80 = 220 Ω \*

R83 = VDR S10K275

P1 = ajustable 100 Ω

P2 = ajustable 1 kΩ

P3 = ajustable 1 kΩ vertical

\* cf. texte

Condensateurs :

C1,C8,C12,C17,C20,C21,C23 à C25,C28,C31 = 100 nF céramique

C2,C3 = 1 μF/16 V tantale vertical

C4 = 1 nF RM (au pas de 5 mm)

C5 = 10 nF

C6, C7,C10 = 22 nF

C9 = 1 nF

C11 = 1 μF/16 V

C13,C19 = 47 μF/16 V

C14,C15 = 10 μF/63 V vertical

C16,C26 = 10 μF/63 V

C18,C27 = 220 μF/35 V vertical

C19 = 47 μF/16 V vertical

C22 = 22 μF/35 V

C29,C30 = 22 pF

Semi-conducteurs :

D1 à D4,D7,D9,D11 à D13,D15 à D17,D19 = 1N4148

D5 = BAT85

D6 = LED à haut rendement

D8 = diode zener 6V8/400 mW

D10 = diode zener 5V6/400 mW

D14,D18 = 1N4001

T1,T3,T10 = BC557B

T2,T9 = BC547B

T4,T5 = BUZ11

T6,T7 = BC548C

T8 = BF245B ou BF256B

THR1,THR2 = TIC116A ou BT151-500R

IC1 = LM324 (DIL14)

IC2,IC6 = LM339 (DIL14)

IC3 = TL431CLP

IC4 = 7806

IC5 = 68HC05C4 (Harris programmé Conrad RFA)

Divers :

JP1 = cavalier

K1 = embase secteur avec fusible 630 mA et interrupteur secteur

K2 = embase autosécable mâle à 2 rangées de 7 contacts

K3 = bornier encartable à 3 contacts au pas de 5 mm

K4,K5 = bornier encartable à 2 contacts au pas de 5 mm

S1 = inverseur unipolaire

S2 = rotacteur 1 circuit/12 positions

S3 = touche unipolaire à contact travail

F1 = POLYFUSE 1A6 (Polyswitch, Conrad Nr. 53 60 83)

Tr1 = transformateur torique 2 x 18 V/3,33 A (tel que, par exemple, amplimo 48014)

X1 = quartz 4 MHz

F2,F3 = fusible 6,3 AT dans porte-fusible

ventilateur de CPU

boîtier tel que Bopla Laboratorium 223 mm x 72 mm x 199 mm (Conrad 52 33 48) avec face avant (Conrad 52 33 72)

module LCD 1 ligne/16 caractères (tel que, par exemple, Sharp LM16155)

4 plaquettes d'isolation TO220 avec canons d'isolation

2 embases téléphone 4 mm

**Figure 2.** Cette platine comporte les composants de puissance de l'électronique de charge.

interconnectés représentent la prise intermédiaire.

Les 10 interconnexions entre les 2 plaques se font à l'aide de fil de câblage souple, l'interconnexion de la masse se faisant à l'aide d'un conducteur multi-brin de section plus importante (comparable à celle d'un conducteur de la liaison au secteur). La fixation de la plaque sur le fond du coffret de même que celle du transformateur torique se fera par le biais d'orifices percés aux points requis dans lesquels passeront les vis de fixation. La fixation de la plaque principale sur la face avant est elle bien plus simple puisqu'il suffit de la glisser dans les rails prévus à cet effet dans la demi-coquille inférieure.

## L'ÉTALONNAGE

Il faut commencer par adapter la résistance R72 au ventilateur de CPU utilisé. Il n'est pas nécessaire, pour cela, d'avoir implanté le contrôleur sur la plaque. On connecte le ventilateur au bornier K4 et on mesure la tension aux bornes de K4. Il faudra, si elle dérive de plus de 1 V de la tension d'alimentation nominale du ventilateur (12 V dans la majorité des cas), adapter la valeur de R72 en conséquence. On peut utiliser, pendant une courte période, une résistance normale de 1/3 W si l'on ne dispose pas de résistances de 2 ou de 5 W. Voici l'approche la plus rapide : commencer par brancher une valeur trop élevée, 47  $\Omega$  par exemple, puis, à la main, placer une seconde résistance en parallèle sur la première et mesurer la tension aux bornes du ventilateur. Commencer avec une valeur élevée et la diminuer progressivement jusqu'à obtenir la tension d'alimentation du ventilateur requise. On détermine ensuite la valeur des composants pris en parallèle et on soude sur la plaque endroit une résistance de 2 W de la valeur ainsi déterminée.

Pour l'étalonnage de la surveillance de température non plus, le contrôleur n'est pas requis. On commence par

**Figure 3. Vue plan-géante sur notre prototype.**

mettre la résistance NTC (à coefficient de température négatif, d'une valeur à froid comprise entre 500 et 1 000  $\Omega$ ) à la température ambiante à laquelle doit se faire la coupure de l'appareil et on mesure sa valeur à ladite température. On donne à R80 la valeur mesurée avant de l'implanter sur la plaque. La NTC sera montée à l'endroit où l'on veut suivre la température, sur le transformateur ou le radiateur par exemple. Il faudra, si l'on veut surveiller la température de l'accu, mettre la NTC sur l'accu lui-même et la fixer par élastique ou

bande Velcro, la température de coupure du système devant se situer aux alentours de

45 °C (celle du transformateur ou du radiateur pourra elle, être choisie entre 60 et 90 °C).

Pour le reste des étapes d'étalonnage, le chargeur d'accus doit être complet (contrôleur et affichage LCD compris). La routine de calibration du microcontrôleur débute de la manière suivante : S1 placé en position « NiCd » (fermé), S2 en position 6 cellules, cavalier JP1 en place, mettre le chargeur sous tension et, par action sur P3, régler le contraste de

**Figure 4. Coup d'œil sur la plaque avant du prototype.**

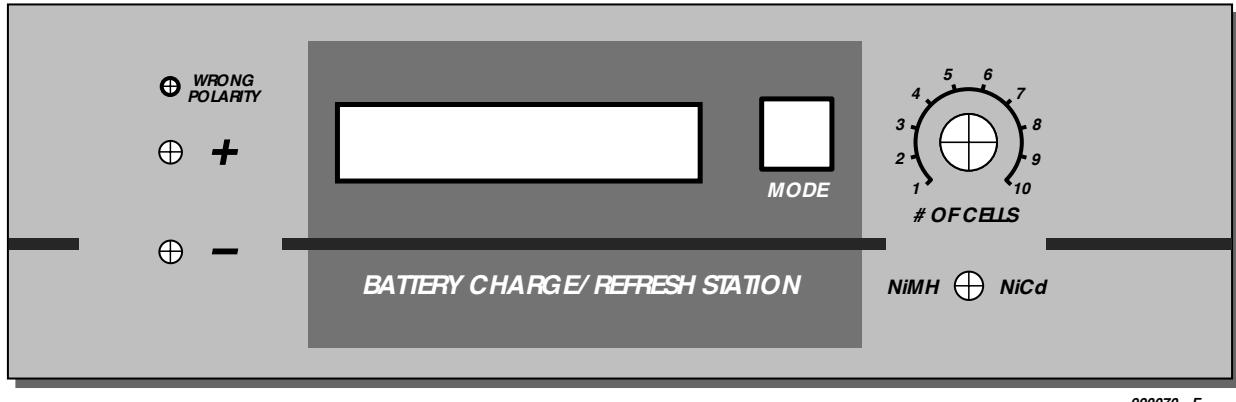

990070 - F

**Figure 5. Proposition de face avant à échelle réduite (75%).**

l'affichage pour la meilleure lecture, il doit indiquer « START SELF-TEST ».

On enlève maintenant JP1.

On prend, pour la suite de la calibration, un multimètre (en calibre 3 à 10 A CC) entre les pôles + et – du connecteur destiné aux accus, K5. Le multimètre mesure le courant de sortie du chargeur qui circule par son intermédiaire.

De par la forme impulsionnelle du courant, un voltmètre efficace vrai (True RMS) donnera une valeur légèrement différente de celle fournie par un multimètre normal, les écarts n'étant cependant pas importants. Voici comment mesurer et régler les courants de charge et de décharge :

1. Appuyer sur S3. L'affichage devrait afficher « CHARGE = 3 A MAX ». Ajuster, par le biais de P2, le courant à 3 A.

2. Appuyer sur S3. On lit sur l'affichage « CHARGE = 2 A MID ». L'instrument de mesure devrait afficher la même valeur que précédemment.

3. Actionner S3. L'affichage indique alors « CHARGE = 1 A MIN ». Le courant mesuré devrait être de 1 A ( $\pm 10\%$ ). Déconnecter le multimètre.

4. Appuyer sur S3. L'affichage dit « ADJUST 1.800 A ». On branche alors un accu chargé (de 4 à 8 cellules) au système et on prend un instrument de mesure mis en calibre 2 A CC en série dans la ligne allant vers l'accu (entre la borne + de K5 et le pôle positif de l'accu). Ajuster, par action sur P1, le courant entre 1,78 et 1,82 A. Déconnecter l'instrument de mesure et l'accu.

5. Appuyer sur S3. On lit sur l'affichage « OVER - VOLTAGE ». Basculer S2 en position 8 cellules. L'affichage indique alors « IN:xxxx EMP:1200 », xxxx

devant être une valeur supérieure à 1 200. Placer maintenant S1 en position « NiMH » (ouvert). xxxx doit alors dépasser 1 800, sinon l'affichage doit indiquer « OVER - VOLTAGE » (la valeur affichée dépend de la tension à vide du transformateur).

6. L'étape suivante consiste à court-circuiter (volontairement) les bornes de connexion de l'accu (+ et – de K5). La valeur visualisée par l'affichage doit être inférieure à 10, l'indicateur d'erreur de polarité (la LED D6 « Wrong Polarity ») doit s'allumer. Supprimer le court-circuit.

7. Appuyer sur S3. Le chargeur se trouve maintenant en mode de fonctionnement normal, l'affichage nous dit, en raison de l'absence d'accu, « NO ACCU TO SERVE ».

## MODE D'EMPLOI

On met le chargeur sous tension sans y avoir connecté d'accu; l'affichage nous dit « NO ACCU TO SERVE », signalant ainsi qu'il est prêt. Tant que l'on n'a pas connecté d'accu au chargeur l'organe de commande S3 reste inactif. On commence par définir, par le biais de S1, le type d'accu et par S2 le nombre de cellules (de 1 à 10), pour ensuite connecter l'accu (ou le set d'accus) à (re)charger au chargeur. On dispose, dès l'apparition sur l'affichage du message « ADJUST: CHARGE », de 5 s pour actionner la touche S3, en vue de changer de programme (cf. l'encadré « Programmes »).

En l'absence d'action sur S3, la CHARGE démarre automatiquement au bout de 5 s. En cas d'action sur S3 on passe, après chaque action sur cette touche, au programme suivant (CYCLE, ALIVE, CHARGE...). Si, 5 s après une action sur S3, il n'y en a pas eu d'autre, le programme du menu est lancé et la charge démarre, ce que l'on constate par l'affichage du message « START CHARGING ». 15 secondes plus tard on voit s'afficher, tout d'abord, la capacité chargée sous la forme :

CCAP= xxmAh

## Capacités

*La référence de l'état d'un accu est la capacité qu'il peut fournir (quantité de courant) exprimée en ampère/heure (Ah) ou milliampère/heure (mAh), capacité variant relativement fortement en fonction du courant de décharge. Plus le courant de décharge est faible, plus les pertes de décharge sont faibles et, partant, la capacité que l'on peut lui demander importante. Il faudra donc toujours s'informer, lors de l'achat, à quel courant de décharge le fabricant spécifie la capacité. On utilise souvent le terme C-Rate qui définit l'intensité du courant (en A ou mA) en tant que partie de la capacité nominale (en Ah ou mAh). Une capacité donnée de 1 Ah à C/10 (0,1 C) signifie que la mesure de la capacité s'est faite à un courant de 100 mA. Si un autre fabricant donne une capacité identique mais à un taux plus élevé (de C/3 ou 0,33 C par exemple), on se trouve, en principe, en présence d'un accu meilleur. En effet, s'il arrive à fournir une capacité de 1 Ah à un courant de décharge de 333 mA, il devrait disposer, à un courant de décharge de 100 mA, d'une capacité dépassant ces 1 Ah.*

*Il est bon de se rappeler, dans le cas de notre chargeur d'accu HP, que ce dernier travaille à un courant de décharge important (1,5 A au début, 0,5 A au minimum après).*

*La capacité mesurée dans ces conditions donne un bon repère sur sa capacité de supporter/fournir des courants importants; elle sera, dans la majorité des cas, quelque peu plus faible que la capacité nominale donnée par le fabricant.*

*La quantité de courant en cours de charge n'apprend pas grand chose en ce qui concerne la capacité de l'accu. Elle est toujours supérieure sachant qu'en fin de charge le courant de charge est, de plus en plus, converti en chaleur et partant perdu.*

On aura, par exemple « CCAP = 1,8mAh », ce CCAP signifiant « *Charged CAPacity* ).

On peut, par action sur la touche de fonction, en cours de charge, appeler les différents affichages suivants : au bout de 2 s on commence par voir apparaître le mode de programme choisi (« CHARGE MODE », « CYCLE MODE » ou « ALIVE MODE »), ensuite, si l'on est en charge, pendant 5 s, la capacité déchargée (« DCAP = 0,0mAh » par exemple DCAP = *Discharge CAPacity*), puis la capacité chargée, CCAP. En l'absence de données de mesure, DCAP lors d'une charge en programme CHARGE par exemple, on aura affichage d'un 0,0.

Lorsque l'accu n'accepte plus de charge additionnelle, le processus de charge est interrompu. Si l'on se trouve en programme CYCLE et ALIVE on aura début de décharge, processus signalé par l'apparition du message « START DISCHARGE » ou, par le message « CHARGER FINISHED » signalisation de la fin de charge et partant de la possibilité de déconnecter l'accu. Il est possible, même après la fin de la charge, d'obtenir, tout comme lors de la charge et de la décharge, l'affichage des valeurs de CCAP et DCAP. On passe d'un affichage au suivant par action sur la touche de commande.

En cas d'interruption du processus de charge (en raison d'un accu défectueux ou d'un set (*pack*) inutilisable), on aura affichage du message « END WITH ERROR ».

Si, après le message « CHARGER FINISHED », on ne débranche pas l'accu, on aura, au bout d'une heure, lancement d'un processus de maintien de charge qui sera annoncé par le message « START TRICKLE ». L'affichage n'indique pas alors la CCAP, mais la TCAP (*Trickle charge CAPacity*) de la capacité additionnelle, la valeur de TCAP n'étant cependant pas mémorisée de sorte qu'une action sur la touche ne fournit que la valeur CCAP de la charge précédente.

Si l'on a, en cours de fonctionnement, activation du dispositif de thermo-protection (à NTC), le programme est interrompu, l'affichage indiquant « OVER-TEMPERATURE ». Au bout de quelque 15 mn le programme est repris, l'affichage indiquant alors « CONTINUE PROGRAM ».

En cas d'interruption du processus à la suite d'une disparition (ou coupure) de la tension secteur, toutes les valeurs et le paramétrage sont stockés en mémoire. Le programme se poursuit partant correctement lors du retour de la tension du secteur, l'affichage indiquant alors « CONTINUE PROGRAM ». Ceci n'est vrai qu'à condition que l'accu connecté ait 4 cellules au minimum et que le secteur ait disparu pendant 20 s au moins. Si l'accu com-

# Programmes

## CHARGE

*Charge rapide standard, l'accu est chargé une unique fois*

## CYCLE

*On a charge, puis décharge et recharge de l'accu*

## ALIVE

*L'accu est chargé, déchargé, rechargé puis redéchargé. Si, en fin de second processus (charge/décharge), la capacité est supérieure à celle mesurée lors du premier, on procède à une nouvelle charge/décharge. Ce processus se poursuit un maximum de 6 cycles (voire moins si l'appareil constate une absence de croissance de capacité). ALIVE se termine par un processus de charge.*

porte moins de 4 cellules, le chargeur se manifeste, avec le message « ADJUST CHARGE », ce qui implique qu'il faudra redémarrer le programme manuellement.

## CONSEILS D'UTILISATION

Si l'on a, après connexion d'un accu, allumage de la LED rouge (D6, *Wrong Polarity*), cela signifie que l'accu est soit branché à l'envers, soit déchargé trop profondément. Dans le premier cas, le message « NO ACCU TO SERVE » reste affiché, il suffit d'inverser la polarité de l'accu. Si, cependant, on voit s'afficher le message « ADJUST CHARGE » c'est que l'accu a été trop déchargé, le processus de charge pouvant se poursuivre normalement comme dans le cas d'un accu n'ayant pas subi de décharge trop profonde (c'est-à-dire sans allumage de LED).

Si l'on a, en début de charge (« START CHARGE ») allumage de la LED rouge, cela signifie que l'accu ou le set d'accu (*pack*) comporte une diode de protection; il faudra connecter l'accu directement c'est-à-dire sans diode.

Dans le cas d'un accu doté d'une thermo-protection par contact bimétal, le déclenchement de ce dispositif se traduit par une interruption du courant de charge, le chargeur affichant « NO ACCU TO SERVE ». En l'absence de mesure complémentaire, le contact se refermant après refroidissement, le chargeur reprend la charge. Même si le contact bi-métal devait s'ouvrir un certain nombre de fois, cela n'empêchera pas l'accu d'être chargé à plein au cours du programme CHARGE, même si c'est avec quelques interruptions. Il n'en reste pas moins que la valeur de CCAP est remise à zéro à chaque fois, de sorte que la valeur affichée représente la charge accumulée depuis la dernière interruption.

Il est interdit de modifier le nombre de cellules et le type d'accu en cours de processus de charge ! Ce paramétrage est à faire avant de brancher l'accu. Il faudra, s'il devait se faire que l'on pro-

cède à une charge avec un paramétrage totalement erroné, déconnecter l'accu et corriger le paramétrage avant de rebrancher l'accu.

On ne peut pas, en raison du courant de charge élevé mis en jeu, utiliser de porte-piles en plastique courant, le contact en spirale de son pôle négatif ne tardant pas à prendre une couleur rouge cerise (échauffement). On ne pourra utiliser, dans le cas d'accus monobloc, que des porte-piles spéciaux prévus pour des courants important. Ce problème de contact ne se pose pas dans le cas de set d'accus (10 cellules au maximum, taille AA au minimum), mais il faudra opter pour des connexions courtes et de section suffisante (1 mm<sup>2</sup> minimum). La charge se fera de préférence à température ambiante de 20 °C, l'accu atteignant ainsi une température maximale de 45 °C. On évitera les températures extrêmes, sans jamais passer en-deçà de 0 °C et au-delà de 40 °C. On réchauffera des accus froids et on laissera le temps au chargeur de prendre sa température de croisière s'il a été stocké à basse température.

La charge des types de cellules les plus petites (mignon) exige un minimum de précaution. La capacité nominale doit, normalement, être supérieure à 700 mAh. Il est bon, en cas de charge de cellules d'un certain âge, de vérifier, au cours de premières minutes au moins, la température des cellules. Si l'accu (déchargé) chauffe de façon importante dès le début il est préférable d'arrêter la charge, sachant qu'il apparaît que l'accu ne supporte plus une charge rapide (résistance interne trop élevée).

Il est préférable de disposer (en respect de l'environnement) d'un tel accu. Il en va de même dans le cas d'un accu avec lequel on voit apparaître le message « END WITH ERROR ». On se souviendra que le cadmium est un métal lourd préjudiciable à l'environnement. Il faudra rapporter les accus aux endroits désignés à cet effet.

(990070-2)

# cours de programmation du BASIC Stamp (3)

## *3ème partie : programmation en BASIC*

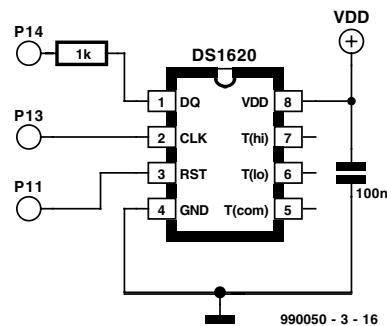

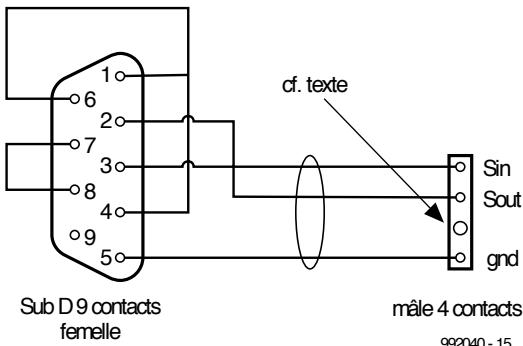

Nous allons, dans le présent article, vous présenter les instructions de branchement et d'accès à l'EPPROM du BASIC Stamp, qui nous serviront à faire suivre un trajet prédéterminé au BOE-Bot. Un mini-haut-parleur piézo constituera le système de réponse servant à identifier la position au cœur de votre programme. Nous vous proposerons également une centrale d'acquisition de température mobile qui pourra servir de projet optionnel destiné à vous apprendre les bases de la communication sérielle synchrone.

par Chuck Schoeffler, Ph. D.,

Ken Gracey et Russ Miller

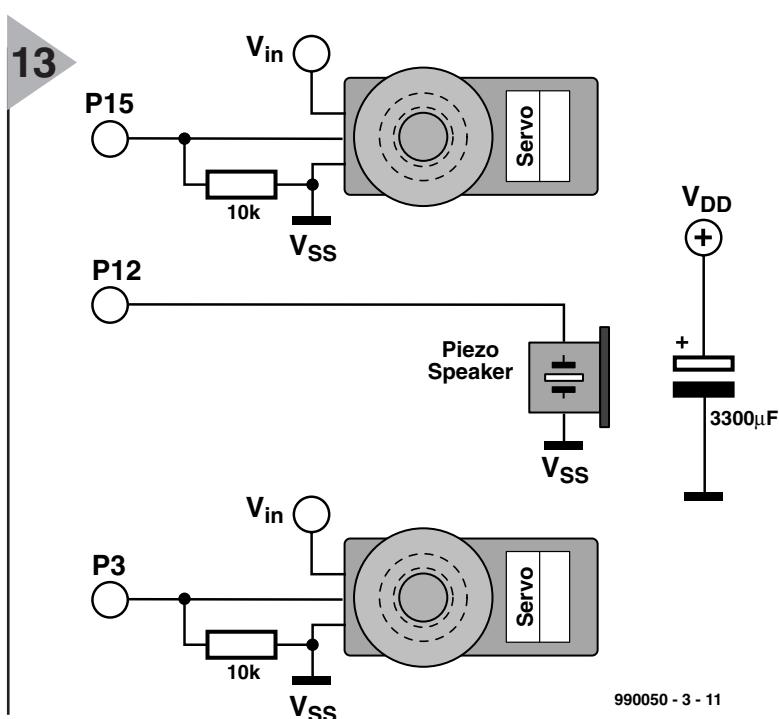

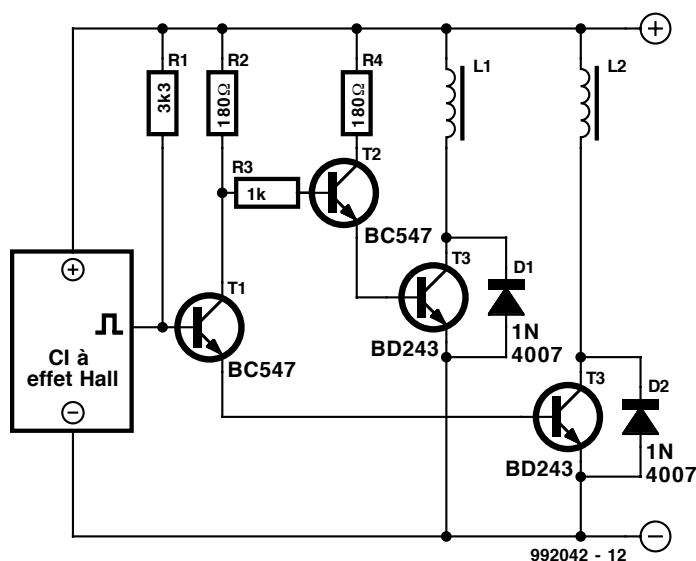

**Figure 13. Schéma de principe de la commande et du système de réponse (feedback).**

### Liste des composants

- 1 BOE-Bot complet (robot basé sur le Board of Education d'Elektor)

- 1 haut-parleur piézo

- 1 condensateur 3 300  $\mu$ F

- 2 résistances de 10 k $\Omega$  (optionnelles)

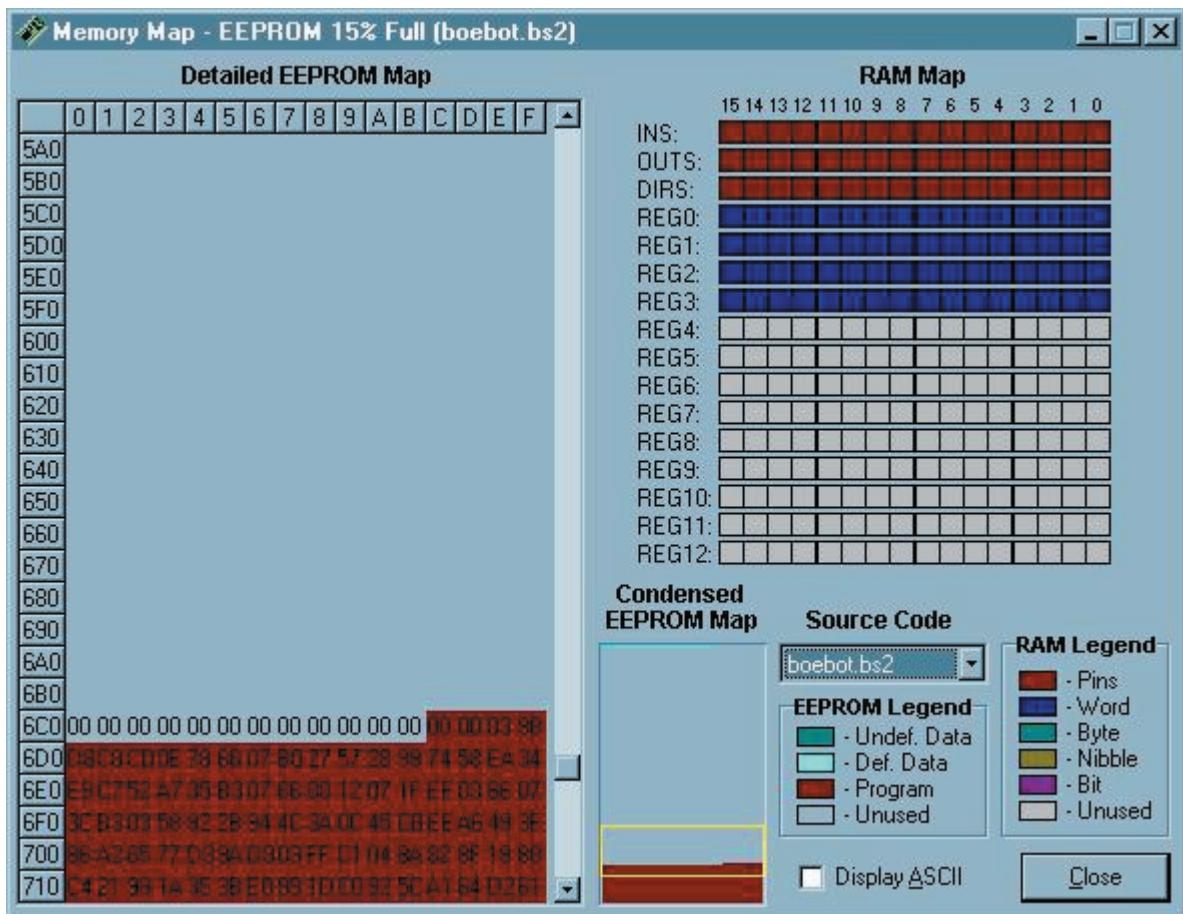

### MOUVEMENT À BASE DE ROUTINES ET DE MÉMOIRE

Le mouvement est l'une des propriétés caractéristiques d'un robot et c'est aussi une approche idéale pour apprendre à structurer et écrire un programme simple en PBASIC. La présente expérience est centrée principalement sur la programmation en BASIC vu que c'est

par son biais que l'on obtient, en l'absence de données fournies par un quelconque capteur, les mouvements du BoE-Bot. Il faut, pour pouvoir structurer son programme de façon à ce que BoE-Bot se mouve comme on l'entend, commencer par comprendre comment appeler des sous-programmes, lire des patterns de déplacement présents en EEPROM, de combien se déplacer par

le biais d'une boucle *for-next* et comment faire pour revenir au point de départ. La liste des composants donne les composants nécessaires pour cette expérience. La **figure 13** montre le schéma de l'électronique utilisée dans le cadre du présent article.

## COUP D'OEIL À LA SERVO-COMMANDE

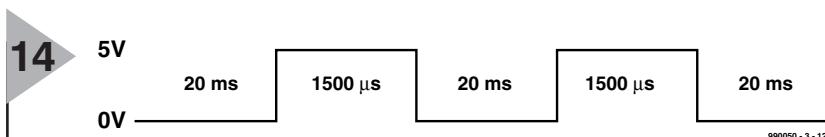

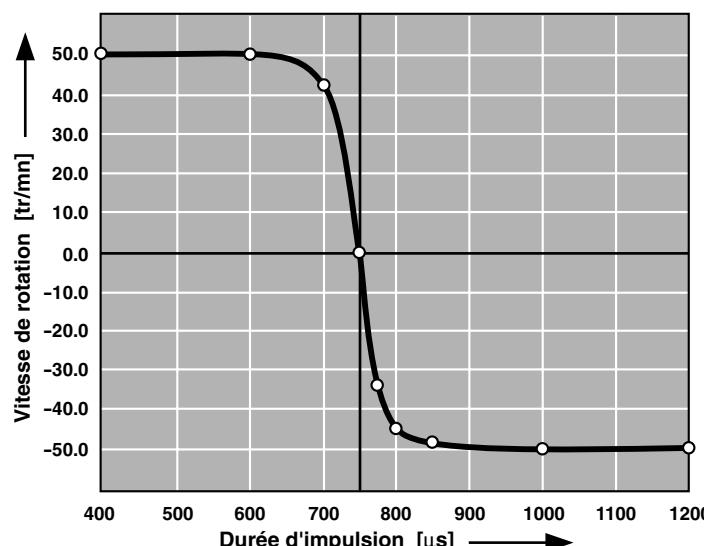

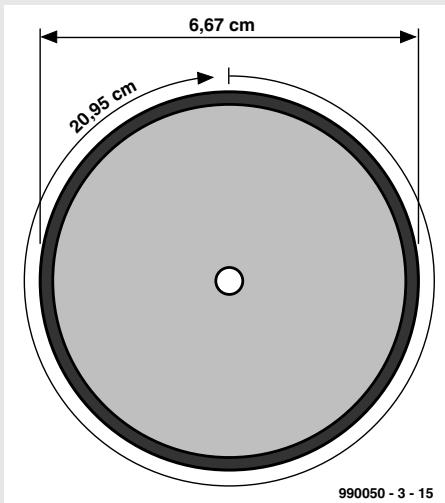

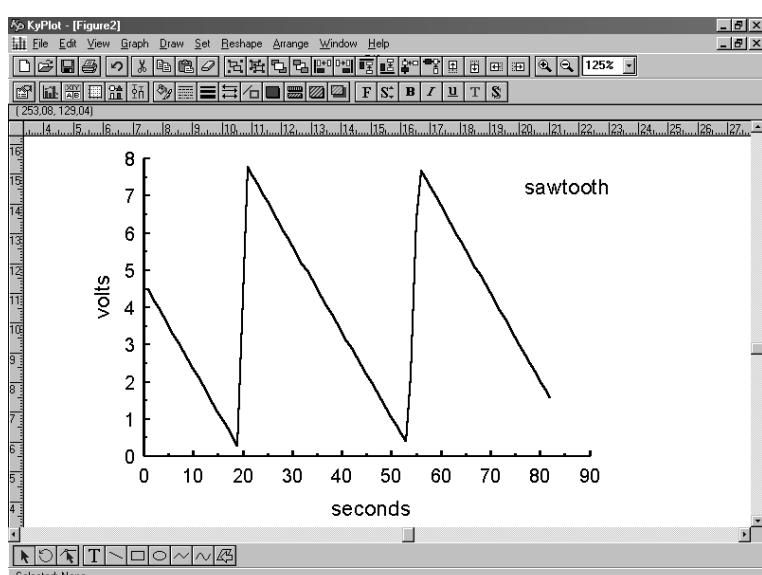

Les servo-commandes sont des composants à boucle fermé comparant en permanence la position qui leur a été demandée (consigne) par le biais de l'instruction *pulsout* du BASIC Stamp, avec leur position effective (proportionnelle à la résistance d'un potentiomètre solidaire de l'axe). Dès qu'apparaît la moindre différence entre les deux, l'électronique intégrée dans la servo commande une rotation du moteur en vue d'éliminer l'erreur. Nous avons modifié l'axe du potentiomètre de la servo jusqu'à ce que les engrenages cessent de tourner lorsque le BASIC Stamp envoie une impulsion de  $1500\ \mu s$ . Une valeur *pulsout* de 750 correspond à  $1500\ \mu s$  (l'instruction fait appel à des unités de  $2\ \mu s$ ). Une valeur supérieure à 750 entraîne une rotation de la servo dans le sens horaire, une valeur inférieure à 750 se traduira par une rotation dans le sens anti-horaire. Une valeur proche de 750, 760 par exemple, produira une rotation très lente. La **figure 14** propose un chronodiagramme de la modulation en largeur d'impulsion (MLI = PWM pour *Pulse Width Modulation*)

On peut faire appel à une boucle *for-next* pour voir l'effet que différentes largeurs d'impulsion ont sur la vitesse de la servo. Mettez votre BoE-Bot sur son nez ou placez-le sur un objet qui l'empêche de se déplacer. Téléchargez le **listage 1** vers votre BASIC Stamp. La **figure 15** rend graphiquement la correspondance entre la largeur d'impulsion et la vitesse de rotation (tr/mn) dans le cas d'une servo Futaba S-148.

## RÉPONSE SONORE

La commande *freqout* du BASIC Stamp peut servir à doter votre BoE-Bot d'une réponse acoustique. Elle a, comme toutes les instructions PBASIC, une syntaxe spécifique qu'il faut respecter si on veut que ça marche. Téléchargez le code suivant dans votre BASIC Stamp pour entendre le haut-parleur se manifester :

```

freqout 12,750,2000

'signal de 2 000 Hz d'une

durée de 750 ms sur P12.

```

On pourra, pour obtenir un son plus « robot », essayer l'exemple du **listage 2**. Cette routine commence par déclarer *Hz* comme variable de mot (*word variable*), c'est-à-dire un nombre compris entre 0 et 65 536. La boucle

**Figure 14. Commande de servo basée sur la modulation en largeur d'impulsion.**

```

'Listage 1

left_servo    con    15

right_servo   con    3

x var word

pause 2000

start:

for x = 650 to 850          'début de routine

pulsout left_servo,x     'largeur d'impulsion de 1 500 us

pulsout right_servo,1500-x 'largeur d'impulsion de 1 500 us

pause 20                  'pause de 20 ms

next

```

```

'Listage 2

Hz var word

for Hz = 1 to 4000 step 1000

freqout 12,70,Hz,4000-Hz

'génère 2 sons de 70 ms sur P12

next

```

s'exécute 4 fois ((4000-1)/1000), générant simultanément 2 fréquences sur P12. La première fréquence passe de 1 à 4 000 Hz, la seconde décroît de 4 000 vers 1 Hz. Vous pouvez doter votre programme de sons de ce genre.

## INSTRUCTION GOTO